ENIAC

L'ENIAC (acronyme de l'expression anglaise Electronic Numerical Integrator And Computer) est en 1945 le premier ordinateur entièrement électronique pouvant être Turing-complet. Il peut être reprogrammé pour résoudre, en principe, tous les problèmes calculatoires.

| Développeur | |

|---|---|

| Fabricant |

Moore School of Electrical Engineering |

| Date de sortie | |

| Date de retrait |

| Type |

Ordinateur électronique programmable, puis ordinateur à programme enregistré |

|---|---|

| Génération |

Première génération |

| Alimentation |

150 kW |

|---|---|

| Processeur |

Circuits logiques à tubes électroniques |

| Mémoire |

Pré-1948 : 20 accumulateurs de 10 chiffres décimaux. Post-1948 : registres et mémoire de 200 chiffres décimaux. 1952 : ajout de mémoire à tores magnétiques de 100 mots de 10 chiffres BCD |

| Dimensions |

170 m2 |

|---|---|

| Masse |

27 tonnes |

Sous l’influence de John von Neumann, l’ENIAC est à partir de 1947 reconverti en ordinateur à programme enregistré, quoique de façon quelque peu plus primitive que les ordinateurs qui lui succéderont. Ainsi, le , l’ENIAC devient également le premier ordinateur électronique à exécuter les instructions d’un programme, ainsi que le premier ordinateur à exécuter, avec quelques limites, un programme fonctionnant en mémoire[1].

Il est précédé en 1941 par le Zuse 3 allemand, une machine programmable mais encore électromécanique (utilisation de relais), et par la série de calculateurs britanniques Colossus, électroniques mais non Turing-complets.

Histoire

Le principe de l'ENIAC vient d'une idée de John William Mauchly, professeur de physique et l'un des deux concepteurs de l'ENIAC. Participant à une conférence à l'Ursinus College, il observe des analystes produire des tables de tir, et se rend compte que ces calculs pourraient être réalisés électroniquement. Il s'associe avec J. Presper Eckert qui conçoit les circuits et résout les problèmes d'ingénierie, le principal étant la durée de vie des tubes électroniques. L'armée américaine, intéressée, finance le projet pour les besoins du laboratoire de recherche en balistique. L'ordinateur est financé le sous le nom Project PX et construit à la Moore School of Electrical Engineering (en) de l'université de Pennsylvanie à partir du 31 mai 1943[2]. La machine entre en opération le et commence à travailler sur des calculs liés à la conception d'armes thermonucléaires[3] - [4].

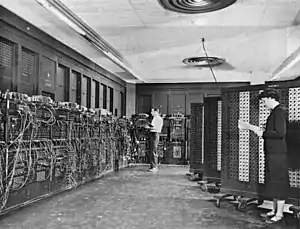

Le , l'ENIAC est dévoilé au public à l'université de Pennsylvanie à Philadelphie. En 1947, il transféré à l'Aberdeen Proving Ground, un laboratoire de l'US Army au Maryland, où il est remis en marche le 29 juillet et commence des calculs de tables de tirs. Il continue à fonctionner jusqu'à son arrêt le 2 octobre 1955[5]. Aujourd'hui, une partie de la machine est conservée à l'université de Pennsylvanie où un petit musée lui est consacré.

L'architecture de l'ENIAC, décidée et gelée en 1943, est novatrice par son parallélisme, sa vitesse et sa Turing-complétude, mais ne permet initialement pas d'enregistrer un programme en mémoire ; la programmation se fait donc par câblage. Toutefois les idées produites par ce travail et l'impact sur des personnes telles que John von Neumann, influenceront profondément le développement des ordinateurs suivants, notamment l'EDVAC, l'EDSAC, l'IAS et le SEAC (en)). Une conversion de la machine en architecture von Neumann, sous la direction de ce dernier, a lieu à partir de 1947 permettant, avec quelques limites, d'enregistrer et exécuter un programme en mémoire[6]. L'ENIAC fonctionnera par la suite dans cette configuration jusqu'à la fin de son exploitation.

Un total de 87 programmes[7] ont été écrits pour l'ENIAC entre 1945 et 1952 : 12 par fonctionnement câblés entre 1945 et 1947, puis 75 par programme enregistré. Les trois dernières années de fonctionnement ne sont pas documentées.

Après l'ENIAC, Eckert et Mauchly fonderont une société, l'Eckert-Mauchly Computer Corporation (en), où ils produiront en 1949 leur premier ordinateur : le BINAC. La firme sera rachetée l'année suivante par Remington Rand pour devenir Univac.

Caractéristiques

L'ENIAC, comme bon nombre d’ordinateurs de première et deuxième génération[8], est une machine décimale, c’est-à-dire utilisant la base 10.

Bien que la logique binaire fût envisagée par les concepteurs, l'utilisation de la logique décimale permet, pour les ordinateurs travaillant avec des cartes perforées (codées au format décimal), d’éviter la conversion des données en entrée et en sortie, donc d’accroître la vitesse de traitement et, pensait-on, nécessiter moins de tubes électroniques[8] - [9]. Il est intéressant de noter que la logique décimale fût de nouveau choisie par Ecker et Mauchly, les concepteurs de l’ENIAC, pour l’UNIVAC I (1951) après un essai peu fructueux avec la logique binaire du BINAC (1949).

L'ENIAC utilise des compteurs à anneaux à dix positions pour enregistrer les chiffres ; chaque chiffre nécessite à cet effet 36 tubes électroniques. L'arithmétique est réalisée en comptant les pulsations avec les anneaux et en générant des pulsations lorsque le compteur fait un tour. L'idée revient en fait à simuler par l'électronique les systèmes de roue à chiffres des machines électromécaniques.

Sa capacité est de vingt nombres à dix chiffres signés permettant chacun de réaliser 5 000 additions simples chaque seconde (pour un total de 100 000 additions par seconde). Il ne peut en revanche gérer en moyenne que 357 multiplications ou 38 divisions par seconde ou trois extractions de racine par seconde. Les entrées-sorties se font au moyen de cartes perforées, à la vitesse de 133 caractères par seconde[10].

L'ENIAC est remarquablement volumineux : il contient 17 468 tubes à vide, 7 200 diodes à cristal, 1 500 relais, 70 000 résistances, 10 000 condensateurs, 300 voyants lumineux pour l'affichage continu de l'état des registres, et environ 5 millions de soudures faites à la main[11]. Deux ventilateurs massifs de 20 cv chacun permettent l'extraction de la chaleur générée par l'ensemble[12]. Son poids est de 30 t pour des dimensions de 2,4 × 0,9 × 30,5 m occupant une surface de 167 m2 (1 800 pieds carrés)[13]. Sa consommation est de 150 kW.

Il utilise des tubes à vide à 8 broches, les accumulateurs décimaux sont réalisés avec des bascules 6SN7, alors que les fonctions logiques utilisent des 6L7, 6SJ7, 6SA7 et 6AC7. De nombreux 6L6 et 6V6 servent de relais pour acheminer les pulsations entre les différents racks d'éléments.

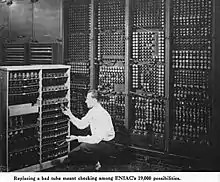

Certains experts en électronique prédirent que les tubes tomberaient en panne si fréquemment que la machine en serait inutilisable. La prédiction n'était que partiellement correcte, de nombreux tubes brûlaient chaque jour laissant l'ENIAC inopérant la moitié du temps. Des lampes plus fiables ne furent disponibles qu'à partir de 1948, Eckert et Mauchly durent donc utiliser des tubes de qualité standard. La plupart des problèmes liés aux tubes se produit au démarrage ou à l'arrêt de la machine car ils sont soumis à un important stress thermique. Le simple fait de ne jamais couper la machine, permet aux ingénieurs de réduire le nombre de pannes à un ou deux tubes par jour. La plus longue période de calcul sans panne est atteinte en 1954 avec 116 heures, ce qui est une prouesse compte tenu de la technologie de l'époque.

Une cause fréquente de panne était la combustion d'un insecte sur un tube chaud, provoquant un stress thermique local et la rupture de l'ampoule de verre. Le terme anglais désignant un insecte est bug. Ce terme, par extension, serait devenu synonyme de dysfonctionnement informatique[14] - [15].

Modules de l'ENIAC de 1945

Dans sa configuration de 1945 et pendant les seize premiers mois de son exploitation, l’ENIAC est un ordinateur modulaire et hautement parallèle[16] de conception proche d'une architecture à flux de données (dataflow). Il comprend quarante modules[17] autonomes répartis ainsi :

Mur gauche

- Unité d’initialisation : Permet d'allumer et éteindre la machine, tester les unités, lancer un programme, et réinitialiser l'état des accumulateurs. Comme chaque unité, l'unité d'initialisation dispose également d'un contrôle de préchauffage des tubes électroniques lors de la séquence de démarrage.

- Unité de cycle : Contient l’horloge maître, cadencée à 100 kHz. Synchronise les modules entre eux et permet l'exécution pas-à-pas pour le débogage. Possède un oscilloscope de contrôle affichant les pulses en circulation dans la machine.

- Programmeur maître (deux panneaux) : Unité de haut niveau permettant de scinder le programme en fonctions, appeler ces fonctions, ainsi que programmer les boucles, les branchements conditionnels et les modifications de séquence dans le programme. Le programmeur maître permet le branchement de 10 actions différentes en fonction de la valeur d'un chiffre[18], de façon analogue à l'instruction « switch » des langages de programmation. Les fonctions, elles, sont implémentées sous forme de dix « steppers » autorisant chacun le lancement d'une séquence de six boucles, et permettant également la création de boucles imbriquées[18]. Cette possibilité de programmer des fonctions, des sauts conditionnels et des boucles imbriquées distingue l'ENIAC de ses prédécesseurs.

- Tables de fonction 1 (deux panneaux) : Larges mémoires mortes contenant les données numériques et les formules du programme. Leur utilisation est générique, elles peuvent également contenir des tables de correspondances, ou trigonométriques ou à tout autre usage pertinent pour le programme.

- Accumulateurs 1 et 2 : Les accumulateurs constituent tant la mémoire que la puissance de calcul de l'ENIAC. Chacun des vingt accumulateurs possède une mémoire de 10 chiffres décimaux, ainsi qu'un circuit d’addition-soustraction à cinq entrées (désignées par des lettres grecques) et deux sorties (A pour addition et S pour soustraction). Ils peuvent également être appairés pour travailler sur des nombres de 20 chiffres décimaux.

- Diviseur et extracteur de racine carrée. Le diviseur-extracteur réquisitionne et pilote les accumulateurs adjacents 2, 3, 5 et 7 pour son fonctionnement[19]. Ces accumulateurs servent au calcul et stockage du numérateur (dividende ou radicande), du dénominateur (diviseur ou racine), du quotient, et un dernier sert enfin de registre à décalage.

- Accumulateurs 3 à 9

Mur face

- Accumulateur 10

- Multiplicateurs 1, 2 et 3. Les multiplicateurs réquisitionnent et pilotent les accumulateurs adjacents 9, 10, 11, et 13 pour leur fonctionnement, avec un mode de fonctionnement similaire à celui du diviseur-extracteur.

- Accumulateurs 11 à 14

Mur droit

- Accumulateurs 15 à 18

- Tables de fonction 2 et 3 (4 panneaux)

- Accumulateurs 19 et 20

- Transmetteur de constantes 1, 2, et 3 : Transmettent à une unité un nombre de 5 entiers signés ou 10 entiers non signés en provenance d’une table de fonction ou d'une carte perforée.

- Imprimante, unités 1, 2 et 3

À cela s’ajoutent trois tables de fonction mobiles pouvant être connectées au tables de fonction 1, 2 et 3, ainsi que deux tabulatrices IBM (une en entrée et une autre en sortie).

Dans l'ENIAC de 1945, chaque module peut être considéré comme une fonction élémentaire (« lire », « effectuer telle opération », « boucler si », « écrire »), chacune paramétrée via un pupitre, et chaînées par câblage d'un module à l'autre. Cette approche est analogue à celle d'une ligne de commandes dont on chaîne par un tube les entrées et sorties d'une séquence de programmes.

Ce paradigme de programmation est simple d'implémentation, parallèle par conception, dispense de mémoire vive pour stocker le programme en exécution, et dispense aussi de processeur devant lire et exécuter séquentiellement des instructions, ce qui accroît la vitesse de calcul (un signal traverse un câble beaucoup plus rapidement qu'un circuit électronique). En contrepartie, le développement des programmes est fastidieux. Tirer parti d'une puissance de calcul distribuée à travers 20 unités n'est pas chose aisée, et d'autre part, le câblage est long et pénible à mettre en oeuvre, difficile à déboguer, et, comme avec une ligne de commandes, complique la création de programmes longs et complexes[18]. En tout état de cause, Maulchy comparait la programmation de l'ENIAC de 1945 à « câbler ensemble vingt calculatrices »[20].

Modules de l'ENIAC de 1948

À partir de 1947, l’ENIAC est recâblé en architecture von Neumann[18] - [21], alors fraîchement inventée. Ses modules ne sont plus utilisables individuellement mais forment ensemble un CPU exécutant les instructions d’un programme enregistré. Le câblage des modules devient permanent, et les rares modifications ne servent qu'à faire évoluer le processeur.

Les modules sont reconfigurés ainsi[22] :

- huit accumulateurs sont recâblés ensemble pour former l’unité arithmétique logique (UAL, ou ALU). Quatre d’entre eux possèdent une fonction spécifique :

- accumulateur 15 : accumulateur principal, au sens moderne du terme,

- accumulateur 13 : accumulateur arithmétique auxiliaire. Permet de stocker les résultats intermédiaires des multiplications, divisions et racines carrées,

- accumulateurs 11 et 15 : caches de données en provenance d’une table de fonction ou d’une carte perforée ;

- programmeur maître : Devient le séquenceur, c'est-à-dire l'unité de lecture et décodage des instructions. Les « steppers » servent à implémenter la boucle de séquencement. Le panneau de soixante fiches de sortie est recâblé et constitue un réseau logique programmable (PLA) de décodage des instructions ;

- trois autres accumulateurs sont attribués aux registres internes du séquenceur : l'accumulateur 8 sert au pointeur d’adresse mémoire, trois chiffres de l'accumulateur 6 servent au compteur de programme, et un dernier sert de registre d’instruction ;

- les neuf accumulateurs restants sont sérialisés et forment la mémoire vive de la machine, destinée aux instructions et aux données. Une mémoire magnétique à tores de ferrite viendra ultérieurement la compléter ;

- tables de fonctions : Enregistrent le code et les données statiques des programmes à la manière d'une ROM. Chaque ligne de chaque table peut contenir jusqu’à six instructions pour un total maximal de 1 900 instructions (les tables de fonctions permettent de coder 3 800 chiffres décimaux, une instruction et son opérande en utilisent au minimum deux). Une partie du code peut aussi résider en mémoire modifiable, quoique cela sera peu fréquent avant l'arrivée de l'extension mémoire. La mémoire des tables de fonctions, des accumulateurs, et plus tard de la mémoire magnétique, est communément adressable et forme la mémoire centrale de l'ordinateur.

Dans cette première configuration n'utilisant que les modules de 1945, l'ENIAC implémente un jeu de 51 instructions.

À partir de mars 1948 arrive un nouveau module, spécifiquement conçu pour le fonctionnement par programme enregistré : l’unité de conversion[23]. Cette unité permet d'accélérer le décodage des instructions, libérant au passage un accumulateur du séquenceur et permettant de réattribuer sa mémoire à la mémoire vive. Elle libère aussi le programmeur maître dont elle reprend le rôle de façon native et optimisée. L'unité de conversion permet également d'étendre le jeu d'instruction à son maximum possible, soit 100 instructions, et, enfin, de permettre le chargement et/ou l'exécution d’un programme depuis le lecteur de cartes perforées[21]. Ce mode de fonctionnement possède néanmoins deux inconvénients : en mode chargement, le programme doit pouvoir entrer dans l'espace mémoire modifiable de l'ENIAC, initialement en quantité très limitée, ce qui restreint donc son usage aux programmes les plus courts. D'autre part, en mode exécution, le programme n'est pas enregistré en mémoire et son exécution dépend donc de la vitesse de lecture des cartes - un mode de fonctionnement analogue aux prédécesseurs de l'ENIAC tel que le Zuse 3.

Début 1952, un dernier module est ajouté : l'unité de décalage à haute vitesse (high-speed shifter unit)[24]. La conversion des modules de 1945 en processeur induisit une certaine pression sur la mémoire de l'ENIAC, incitant à enregistrer plusieurs valeurs dans chaque accumulateur. Ceci nécessite une opération de décalage pour lire la plage de mémoire correspondante, et en conséquence bon nombre d'instructions s'avèrent être des instructions de décalage, qui ne sont pas particulièrement rapides. Cette nouvelle unité multiplie par cinq la vitesse des décalages, permettant une nouvelle amélioration de la vitesse d'exécution des programmes.

Conversion en ordinateur à architecture Von Neumann

Dans sa version de 1943, l’ENIAC est un ordinateur électronique complexe, rapide, et parallèle : un train de pulses circule de façon décentralisée dans des unités largement autonomes[25]. En particulier, chaque accumulateur est doté de son propre additionneur ainsi que d'une mémoire constituée de tubes électroniques, complexe et onéreuse mais beaucoup plus rapide que les lignes de délai fréquemment utilisées à l'époque.

En juin 1944, Herman Goldstine informe John von Neumann de l’existence de l'ENIAC au détour d’une conversation[26]. Von Neumann, alors à pied d’œuvre au sein du projet Manhattan, n’est que trop conscient des besoins d’un calculateur électronique.

Von Neumann rejoint l’équipe de l’ENIAC la même année, alors que la construction de la machine est déjà bien entamée[27]. En hiver 1944 et printemps 1945, il tient des réunions hebdomadaires avec Ecker et Mauchly (créateurs de l'ENIAC) sur la façon de créer un ordinateur à programme enregistré[28]. Ils ébauchent ensemble un concept de machine de Turing universelle dont les instructions sont codées numériquement, puis pouvant exécuter ces instructions pour lire et écrire programmatiquement des données. Leur concept prend rapidement le nom d'EDVAC - Electronic Discrete Variable Automatic Computer.

Le , von Neumman publie le « First Draft of a Report on the EDVAC (en) », définissant pour la première fois les caractéristiques de l’ordinateur moderne et de l’architecture éponyme. Si l’ENIAC n’y est pas mentionné pour des raisons de confidentialité militaire, la conception de l’EDVAC en prend résolument le contrepied : une implémentation logique minimaliste avec une UAL rudimentaire (en comparaison, l’ENIAC possède même un circuit de calcul de racine carrée), un seul accumulateur plutôt que vingt, une conception centralisée plutôt que parallélisée, ou encore la possibilité d’exécuter un programme sous forme d’instructions plutôt qu'en chaînant des fonctions logiques par câblage, et à cet effet, l’installation d’une large quantité de mémoire destinée tant aux instructions qu’aux données.

En 1947, il devient clair que l’EDVAC est encore loin de voir le jour – il ne sera terminé qu’en 1951 – et les besoins en calcul sont toujours aussi pressant. Au printemps de la même année, von Neumann réalise que les unités de l’ENIAC constituent un « kit » permettant de concevoir un ordinateur au sens contemporain du terme, c’est-à-dire à programme enregistré (exécutant des programmes sous forme d'instructions et non en câblant ensemble des modules).

Le nouvel ENIAC prendrait la forme d’une machine virtuelle à architecture von Neumann câblée de façon permanente au dessus de la machine existante. Le recâblage définitif formerait l'interpréteur microcodé de cette machine virtuelle[1] - [29].

Avec cette conversion, certains accumulateurs seraient reconvertis pour former l'UAL. D’autres serviraient de registres pour le compteur de programme, les registres d’adresse et d’instruction, ou encore l’accumulateur principal. D’autres accumulateurs seraient sérialisés et serviraient de mémoire principale. Enfin, les autres unités seraient recâblées en séquenceur permettant le « fetch » et le décodage des instructions. Au passage, l’ENIAC devenu ordinateur à programme enregistré perdrait son parallélisme et donc une partie de sa vitesse, ainsi qu'une faible quantité de mémoire désormais allouée aux registres internes du séquenceur.

Le projet est lancé en avril 1947. Von Neumann conçoit un premier jeu de 51 instructions remarquablement similaire au jeu d’instructions de l’EDVAC, et la conversion débute[22].

La conversion de l’ENIAC en ordinateur à programme enregistré va connaître plusieurs révisions, voyant le jeu d’instructions, à l'époque appelées « ordres », passer de 51 à 60, puis 79, et enfin 83 instructions. La machine étant recâblable, il est possible de librement mettre à jour le jeu d'instructions à la manière des microcodes contemporains. Certaines d'entre elles tirent parti des circuits arithmétiques sophistiqués de l'ENIAC et permettent le calcul de division, racines carrées ou encore de valeur absolue[30], ce qui permet un code plus dense et économe en mémoire vive.

La conversion se termine le avec l'arrivée de l'unité de conversion (Converter Unit), permettant notamment le chargement de programmes depuis le lecteur de cartes perforées IBM[21].

Le , l'ENIAC exécute ses premières instructions, et le , son premier programme[1] - [31]. Les problèmes de fiabilité initialement rencontrés à l'exécution du code sont résolus en réduisant la vitesse d’horloge de 100 kHz à 60 kHz[32], ce qui reste toutefois élevé pour l’époque. À titre de comparaison, la vitesse d'horloge des Colossus était de 5 kHz, et celle du Zuse 3 de 5 à 10 Hz.

Le , l'ENIAC exécute sans dysfonctionnement son premier programme de production : une simulation Monté Carlo de 840 instructions destinée à la fission nucléaire[31]. Un diagramme est aujourd'hui conservé et disponible en ligne comme témoin du premier programme enregistré connu[33], ainsi que son code source[34] - [35].

Le , le Manchester SSEM (Machine Expérimentale à Petite Échelle), un prototype de démonstration, exécute à son tour son premier programme : un test de dix-sept instructions permettant de trouver le plus grand diviseur d'un entier.

L’ENIAC fonctionnera les sept années suivantes de sa carrière comme ordinateur à programme enregistré, où il servira tant à des calculs de fission nucléaire que de prévisions météorologiques[36].

Avant 1952, la qualification de l'ENIAC post-1948 en architecture de von Neumann a pu être sujette à caution, car les instructions des programmes et les données ne partagent pas un espace mémoire entièrement modifiable. Nicholas Metropolis, auteur de la simulation Monté Carlo, parlait ainsi de l'ENIAC comme « premier ordinateur à programme enregistré en lecture seule » (« the first computer to operate with a read-only stored program »)[37], par opposition aux ordinateurs suivants permettant d'exécuter du code automodifiable. En effet, dans l'ENIAC, la mémoire des programmes n’est modifiable que par intervention humaine, agissant donc comme une mémoire morte, ce qui empêche théoriquement l’exécution de code automodifiable. L’EDVAC, de conception minimaliste et dont l'ébauche servit de modèle à l'ENIAC recâblé, ne possédait pas d’instruction de branchement conditionnel : chaque programme devait modifier de lui-même l’adresse des branchements au fil de son exécution. Cette impossibilité apparente de l’ENIAC de faire fonctionner du code automodifiable contraindra von Neumann à revoir sa copie et implémenter les branchements conditionnels dans son jeu d'instruction, qui seront repris ensuite sur l’IAS.

Néanmoins, il a depuis été démontré, et vérifié par émulation, que l'ENIAC dans sa configuration de 1948 supportait déjà l'adressage indirect et donc la possibilité d'utiliser des sous-routines pour enregistrer et récupérer des données depuis des adresses mémoire modifiables, permettant de fait le code automodifiable[29]. Cette capacité était semblerait-il inconnue des concepteurs de l'époque ; Arthur Burks en particulier pensait l'ENIAC de 1948 d'une capacité technique inférieure à celle de l'EDVAC (une machine encore théorique), ce qui s'avérait faux.

En 1951 apparaît la mémoire à tores magnétiques, et l’ENIAC, avec le MIT Whirldwind, est en 1952 le premier ordinateur à en être doté[38] - [39]. Cette mémoire vive de 100 mots de dix chiffres BCD où peuvent être stockées de façon modifiable tant les instructions que les données du programme classe alors définitivement l'ENIAC comme ordinateur à architecture von Neumann.

Avec cette ultime évolution et pour les trois années restantes de sa carrière, rien ne distinguera conceptuellement l’ENIAC de l'EDVAC, et donc d'un ordinateur contemporain.

Comparaison avec les autres ordinateurs

L’ENIAC se distingue de plusieurs façons des ordinateurs de son époque :

- les Colossus sont des machines binaires, électroniques, et programmables par câblage. Toutefois, contrairement à l'ENIAC, ils ne sont pas Turing-complets, et ne possèdent pas une architecture à programme enregistré, même en lecture seule, contrairement à l’ENIAC en configuration de 1948 ;

- le Zuse 3, le Harvard MARK I et l’IBM SSEC sont des machines à relais, donc électromécaniques plutôt qu'électroniques. Contrairement à l'ENIAC de 1945, ces machines sont programmables par instructions plutôt que par câblage. Toutefois, contrairement à l'ENIAC de 1948, aucune ne fonctionne par programme enregistré (exécuté depuis la mémoire de l'ordinateur). À la place, les programmes sont exécutés directement depuis des rubans perforés, conditionnant leur vitesse d'exécution à la vitesse de lecture des rubans. Le Zuse 3 et le MARK I ne disposent par ailleurs pas de possibilité de branchement conditionnel et ne sont pas reconnus Turing-complet. En 1997, un professeur universitaire allemand trouva un moyen détourné d'obtenir la Turing-complétude sur le Z3 en calculant de façon spéculative tous les résultats possibles pour une opération[28]. Néanmoins, cette méthode n'étant guère employable en usage réel, le Zuse 3 n'est considéré Turing-complet que de façon théorique ;

- les Manchester SSEM et l’EDSAC, apparus après l'ENIAC, sont des machines électroniques, binaires, à programme enregistré et architecture von Neumann, c’est-à-dire des ordinateurs au sens contemporain du terme. Une comparaison technique de ces deux machines avec l'ENIAC de 1948 est donc particulièrement pertinente.

Comparaison avec le Manchester SSEM

Le SSEM, également connu sous le nom de « Baby », est un prototype du Manchester Mark 1 ainsi qu'un démonstrateur technique des tubes de Williams. Il est doté d’une architecture von Neumann, d'une mémoire de 32 mots de 32 bits (1024 bits, soit 128 octets), et d’un jeu de sept instructions.

Le SSEM exécuta ses premières instructions en , seulement deux mois après l'ENIAC, ce qui le classe parmi les premiers ordinateurs à programme enregistré, et vraisemblablement le premier à être conçu à cet effet plutôt que converti en cours de route.

Si l'architecture du SSEM est résolument plus traditionnelle que celle de l'ENIAC, une machine de von Neumann implique que le code et les données résident dans le même espace mémoire. Or à cet effet, les 128 octets de mémoire du SSEM ne laissent de place, en sacrifiant les données, que pour 32 instructions. Ce problème est renforcé par l’extrême minimalisme du jeu de sept instructions, nécessitant l’emploi d’une grande quantité d’instructions, et donc de mémoire, pour effectuer une opération donnée. L'EDVAC prévoyait à cet effet une large quantité de mémoire vive permettant de stocker plus de 8 000 instructions, contre environ 1 500 pour l'ENIAC en 1948. Le SSEM, en tant que démonstrateur à petite échelle, n'est pas pleinement fonctionnel et donc plus éloigné de la vision de l’EDVAC que l'ENIAC.

De même, le « First Draft of a Report on the EDVAC » est explicite sur la nécessité de pouvoir enregistrer des résultats sur un support externe, puis de pouvoir les réintégrer dans la machine. Cela était possible avec les cartes perforées de l’ENIAC, qui pouvait d’ailleurs exécuter directement un programme depuis des cartes perforées, mais pas pour le SSEM.

Ces défauts de jeunesse seront corrigés avec le Manchester Mark 1 en .

Comparaison avec l’EDSAC

L’EDSAC est généralement reconnu comme étant le premier ordinateur à programme enregistré conçu à cet effet (contrairement à l'ENIAC), et pleinement fonctionnel (contrairement au SSEM). Un titre qu'il peut également disputer au Manchester Mark 1, finalisé un mois plus tôt mais n'ayant exécuté sa première instruction qu'un mois après. L’EDSAC est devenu opérationnel en mai 1949, et, comme l’ENIAC, rapidement utilisé à des fins de calcul scientifique.

Le jeu d’instructions de l’ENIAC est relativement comparable à celui de l’EDSAC en capacité, et les deux sont très supérieurs aux sept instructions du Manchester SSEM. Les instructions de l’ENIAC et leurs opérandes sont codées sur une taille de mot dynamique de deux à huit chiffres décimaux, contre une allocation statique d’un mot de 17 bits pour l’EDSAC. Le format d’instruction compact de l’ENIAC possède de plus des instructions relativement avancées d’arithmétique et d’entrées/sorties (multiplication et division, extraction de racine carrée, lecture et écriture des données d'une carte perforée…), qui nécessitent un plus grand nombre d’instructions sur l’EDSAC pour effectuer la même opération. À taille de mémoire égale, ceci offre le potentiel d’héberger des programmes plus complexes. Désavantagé par la moindre compacité du code, il n’est pas acquis que l’EDSAC, dont la quantité de mémoire était déjà moindre que l'ENIAC, aurait pu faire tenir en mémoire les 840 instructions de la simulation Monté Carlo exécutée un an plus tôt sur l’ENIAC, et encore moins en conservant de la place pour les données[40].

La mémoire de l’EDSAC est entièrement modifiable, tandis que les programmes de l’ENIAC résident dans une mémoire majoritairement en lecture seule. Cela reste toutefois à nuancer car sur l’ENIAC, l’adresse des branchements du code est enregistrable sur la mémoire modifiable, elle-même adressable logiciellement - les deux sont donc Turing-complet.

L’EDSAC possède une réelle avancée par rapport à l’ENIAC : la présence d’une routine d'amorçage câblée. Sur l’ENIAC, le chargement d’un programme nécessite de saisir l'ensemble de ses instructions sur un pupitre de contrôle, tandis que l’EDSAC peut les charger automatiquement. Ceci permet également la ré-allocation automatique des sous-routines en mémoire, ce dont l’ENIAC est incapable, même en chargeant le programme depuis des cartes perforées.

L’EDSAC est enfin une machine beaucoup plus simple de conception et donc plus fiable, tout en approchant de la vitesse de calcul de l'ENIAC.

Comparaison synthétique

Le tableau suivant[41] - [42] permet de mettre en perspective les capacités de l'ENIAC dans ses configurations de 1945 et 1948 par rapport à l'EDVAC, l'EDSAC et le Manchester SSEM :

| EDVAC | ENIAC

(1945) |

ENIAC

(1948) |

Manchester SSEM | EDSAC | |

|---|---|---|---|---|---|

| Mise en service | Concept : 1945

Implémentation : 1951 |

Décembre 1945

Janvier 1946 |

12 avril 1948 | 21 juin 1948 | 6 mai 1949 |

| Vitesse d'addition | N/A | 200 µs par accumulateur.

Parallélisable 20x |

1200 µs | 2880 µs | 1500 µs |

| Mémoire adressable | 8192 mots de 32 bits

(262 000 bits) |

4000 chiffres décimaux

(équivalent 12 800 bits). Données seulement. 200 chiffres en écriture (équivalent 640 bits) |

Idem configuration de 1945 (équivalent 12 800 bits).

Mémoire partagée par les programmes et les données. Ajout d'une mémoire à tores magnétiques de 100 mots de 10 chiffres BCD en 1952 |

32 mots de 32 bits

(1024 bits) |

512 mots de 17 bits

(8704 bits) |

| Taille maximale d'un programme | 8192 instructions | N/A | Maximum théorique : 1 900 instructions.

Maximum pratique estimé : 1 460 (2,6 chiffres décimaux en moyenne par instruction) |

32 instructions | 512 instructions, dont une partie utilisée par la routine d'amorçage (« initial orders ») |

| Chargement des programmes | Non spécifié | Par câblage depuis diagramme | Par boutons rotatifs

ou par cartes perforées |

Par interrupteurs à bascule | Par ruban perforé |

| Programme traditionnellement exécutés depuis | Lignes à délai au mercure | Câblage ad-hoc | Tables de fonctions

(mémoire en lecture seule) Mémoire électronique des accumulateurs (partiellement) |

Tubes de Williams | Lignes à délai au mercure |

| Entrées/sorties | Conceptuel

seulement |

Cartes perforées : 133 caractères / seconde | Idem configuration de 1945 | Entrées par interrupteurs, sortie par visualisation sur tube de Williams |

|

| Jeu d'instructions | 8 instructions | N/A |

60 instructions, ultérieurement porté à 83 instructions |

7 instructions | 17 instructions |

| Taille de mot d'instruction | 32 bits | N/A | 2 à 8 chiffres décimaux

(équivalent 7 à 25 bits) |

16 bits | 17 bits |

| Branchement conditionnel | Par code automodifiable | Câblage ad-hoc

(« null program ») |

Instruction dédiée | Instruction dédiée | Instruction dédiée |

| Adressage indirect | Par code automodifiable | N/A | Code en lecture seule (avant mémoire magnétique), mais adresses des branchements possibles en mémoire modifiable programmatiquement | Par instruction de transfert établissant l'adresse du saut ou l'incrémentation du compteur de programme | Par code automodifiable |

Performance de l'ENIAC

D'un point de vue théorique, l'ENIAC de 1945 possède une puissance de calcul insolite pour son époque, permise par ses vingt unités de traitement parallèles, un très grand nombre de tubes électroniques, et une programmation par câblage qui épargne les temps de lecture et décodage d'instructions. Avec une capacité de 5000 additions par seconde parallélisées sur ses 20 accumulateurs, sa puissance de calcul brute atteindrait les 100 000 additions par seconde, comparable à celle d'un ordinateur transistorisé tel que le DEC PDP-1[43], pourtant sorti en 1959 et cadencé à une vitesse de 200 kHz.

Dans une présentation[44], l'Institut de recherche en informatique et systèmes aléatoires (IRISA) estime à 50 kFLOPS (50 000 opérations en virgule flottante par seconde) la puissance de calcul théorique de l'ENIAC, bien que cette valeur, toute aussi insolite pour les années 1940, soit à prendre avec précaution puisque la machine utilise un système décimal sans virgule.

En pratique, l'architecture de l'ENIAC de 1945, trop focalisée sur la seule puissance de calcul à sa conception, est fortement handicapée par son absence de mémoire vive. Même s'il n'est pas nécessaire en configuration câblée d’enregistrer le programme en mémoire, cette absence conduit, sauf optimisations complexes, à devoir réserver un accumulateur pour le stockage d'une variable sans pour autant nécessiter sa capacité de calcul, et l'ENIAC de 1945 ne travaille donc typiquement qu'à une fraction de ses capacités. De plus, le parallélisme apporte un surcroît de puissance de calcul, déjà abondante sur l'ENIAC, tout en réduisant encore la mémoire très limitée disponible pour les autres files d'exécution. Ce parallélisme est également handicapé par le goulot d'étranglement causé par une unique file d'entrées-sorties, par la complexité inhérente au traitement parallèle[45], et par la difficulté de conception de programmes câblés. Finalement, un seul programme saura en tirer parti[16] durant la brève carrière de l'ENIAC de 1945, les autres utiliseront un fonctionnement séquentiel plus traditionnel.

Pour ces différentes raisons, une estimation plus réaliste des performances en usage réel de l'ENIAC de 1945 pourrait graviter plus probablement autour de 500 FLOPS[46] - [47], une valeur plus conforme aux ordinateurs de son époque.

L'ENIAC à programme enregistré de 1948, dépourvu d'architecture parallèle et devant lire et exécuter des instructions, est en théorie considérablement plus lent que celui de 1945 : environ 850 additions par seconde (1200 μs par addition) - une performance proche de celles de l'EDSAC et du Manchester Mark 1, mais ironiquement supérieure à la performance en usage réel estimée pour l'ENIAC de 1945. En effet, la configuration de 1948 est équilibrée : la machine utilise de-facto la capacité de l'ensemble de ses modules (qui constituent le processeur), dispose séparément d'une large mémoire centrale formée par la concaténation des tables de fonctions et des accumulateurs, et permet d'écrire facilement des programmes complexes. À cet effet, il n'a pas été démontré que les simulations nucléaires et météorologiques poussées fonctionnant sur l'ENIAC de 1948 auraient pu fonctionner par câblage sur l'ENIAC parallèle de 1945, ni le faire avec le même niveau de performance.

Comparaison de vitesses de calcul

Ce tableau comparatif des vitesses de calcul[48] permet de se rendre compte de l'avancée que représente l'ENIAC par rapport aux moyens de calculs disponibles jusqu'alors.

| Moyens employés | Vitesses de multiplication de nombres de 10 chiffres | Temps de calcul d'une trajectoire d'une table de tir |

Gain de vitesse

par rapport à la génération précédente |

|---|---|---|---|

| Homme à la main, ou machine de Babbage | 5 min | 2,6 j | N/A |

| Homme avec calculateur de bureau | 10 à 15 s | 12 h | x20 |

| Harvard Mark I (électromécanique) | 3 s | 2 h | x4 |

| Model 5 (électromécanique) | 2 s | 40 min | x1,5 |

| Analyseur différentiel (analogique) | 1 s | 20 min | x2 |

| Harvard Mark II (électromécanique) | 0,4 s | 15 min | x1,5 |

| ENIAC (électronique) | 0,001 s | 3 s | x400 |

Reconnaissance

Programmeuses

.jpg.webp)

Entre 1944 et 1955, six femmes, Kathleen Antonelli, Jean Bartik, Betty Holberton, Marlyn Meltzer, Frances Spence et Ruth Teitelbaum sont les premières personnes à programmer l'ENIAC, pour un calcul balistique. Elles sont toutes mathématiciennes. Betty Holberton est en plus journaliste, ce qui lui permettait de voyager. Kathleen Antonelli et Frances Spence sont recrutées en 1942 par l’armée américaine pour calculer manuellement les trajectoires de tir. Marlyn Meltzer et Ruth Teitelbaum sont également calculatrices. Elles travaillent sur l'ENIAC à partir de 1944. Il s'agit d'identifier les différentes étapes du calcul et ensuite de câbler physiquement la machine. Ruth Teitelbaum, Frances Spence et Kathleen Antonelli poursuivirent leur travail sur l’ENIAC lorsque celui-ci est transféré à Aberdeen en 1947[49]. Jean Bartik et Betty Holberton en particulier, rejoindront ensuite une autre femme, Adele Golstine, qui formeront ensemble l'équipe principale de programmation de l'ENIAC à programme enregistré à partir de 1948[20].

Longtemps oubliées de l'histoire, le documentaire The Computers réalisé en 2013 par Kathy Kleiman rend hommage aux six programmeuses[50].

ENIAC-on-a-chip

En 1996, en l'honneur du cinquantième anniversaire de l'ENIAC, l'Université de Pennsylvanie, où l'ENIAC fût construit, sponsorisa un projet nommé « ENIAC-on-a-chip », consistant en la création d'un microprocesseur de 7,44 × 5,29 mm implémentant les fonctionnalités de l'ENIAC dans sa configuration de 1945[51] - [52] - [53].

Comme l'ENIAC, la puce implémente des unités logiques autonomes précâblées, et un logiciel externe permet de configurer sur la puce le câblage spécifique d'un programme.

Bien que cadencé à une vitesse de 20 MHz (contre 100 kHz pour l'original) et considérablement plus rapide que l'ENIAC, il n'avait pourtant qu'une fraction de la vitesse des microprocesseurs de la fin des années 1990.

L'ENIAC a célébré son 70e anniversaire le [54].

Galerie

Quatre modules de l'ENIAC exposés à la Moore School of Engineering. De gauche à droite : table de fonction no 3, l'unité de cycle, l'accumulateur no 16 et le premier panneau du programmeur maître. À l'extrême gauche, tronquée : table de fonctions mobile étendant la table de fonction no 3.

Quatre modules de l'ENIAC exposés à la Moore School of Engineering. De gauche à droite : table de fonction no 3, l'unité de cycle, l'accumulateur no 16 et le premier panneau du programmeur maître. À l'extrême gauche, tronquée : table de fonctions mobile étendant la table de fonction no 3..jpg.webp) Détails de panneaux d'accumulateurs exposés à Fort Sill, Oklhahoma

Détails de panneaux d'accumulateurs exposés à Fort Sill, Oklhahoma.jpg.webp) Vue détaillée d'un module d'accumulateur

Vue détaillée d'un module d'accumulateur Vue détaillée du panneau arrière d'un accumulateur, montrant les tubes électroniques

Vue détaillée du panneau arrière d'un accumulateur, montrant les tubes électroniques_-_Computer_History_Museum.jpg.webp) ENIAC-on-a-chip (ENIAC sur une puce), Université de Pennsylvanie, 1995, au Musée de l'Histoire de l'ordinateur

ENIAC-on-a-chip (ENIAC sur une puce), Université de Pennsylvanie, 1995, au Musée de l'Histoire de l'ordinateur

Notes et références

- (en) Thomas Haigh, « Engineering “The Miracle of the ENIAC”: Implementing the Modern Code Paradigm », ENIAC in Action, (lire en ligne)

- « Key Events in the Development of the First General Purpose Electronic Digital Computer, the ENIAC : History of Information », sur www.historyofinformation.com (consulté le )

- Richard Rhodes, Dark Sun: The Making of the Hydrogen Bomb, , 251 p., « chapter 13 » :

« The first problem assigned to the first working electronic digital computer in the world was the hydrogen bomb. […] The ENIAC ran a first rough version of the thermonuclear calculations for six weeks in December 1945 and January 1946. »

- McCartney 1999, p. 103: "ENIAC correctly showed that Teller's scheme would not work, but the results led Teller and Ulam to come up with another design together."

- Martin H. Weik, « The ENIAC Story », American Ordnance Association, Washington, DC, january–february 1961 (lire en ligne [archive du ], consulté le )

- From Calculus to Computer, édité par Amy Shell-Gellasch et Dick Jardine, édition MAA, p. 145.

- (en) W.B. Fritz, BRL Memorandum Report No. 617: A Survey of ENIAC Operations and Problems: 1946–52, Ballistics Research Laboratory,

- « The Old Days: Decimal Machines », sur www.quadibloc.com (consulté le )

- « Eniac-on-a-Chip Project », sur www.seas.upenn.edu (consulté le )

- « L'ENIAC », sur Aconit.INRIA.

- (en) ENIAC: A Pioneering Computer sur le site de Public Broadcasting Service.

- (en) Nancy Owano et Tech Xplore, « ENIAC panels go on display at Oklahoma museum », sur techxplore.com (consulté le )

- Lire en ligne.

- A priori, il s'agirait plutôt d'un insecte dans un relais Mark I que sur un tube de l'ENIAC. En outre, ce terme a été utilisé par Edison en 1878.

- Passeport pour les médias de demain.

- (en) Arnold Beckmann, Costas Dimitracopoulos et Benedikt Löwe, Logic and Theory of Algorithms: 4th Conference on Computability in Europe, CiE 2008 Athens, Greece, June 15-20, 2008, Proceedings, Springer, (ISBN 978-3-540-69407-6, lire en ligne)

- (en) H. H. Goldstine, « The Electronic Numerical Integrator and Computer (ENIAC) », Institute for Advanced Studies, , p. 1 (lire en ligne

[PDF])

[PDF]) - Brian L. Stuart, « Programming the ENIAC [Scanning our Past] », Proceedings of the IEEE, vol. 106, no 9, , p. 1760–1770 (ISSN 1558-2256, DOI 10.1109/JPROC.2018.2843998, lire en ligne, consulté le )

- Brian L. Stuart, « Simulating the ENIAC [Scanning our Past] », Proceedings of the IEEE, vol. 106, no 4, , p. 761–772 (ISSN 1558-2256, DOI 10.1109/JPROC.2018.2813678, lire en ligne, consulté le )

- « Oral-History:Jean Bartik », sur ETHW, (consulté le )

- W. Barkley Fritz, « Description and Use of the ENIAC Converter Code », Technical Note, no 141, (lire en ligne)

- (en) Thomas Haigh, ENIAC in Action, The MIT Press, , 348 p. (ISBN 9780262033985), p. 153, ch.7, "Converting the ENIAC"

- « A Logical Coding System Applied to the ENIAC -- Section 8 », sur web.archive.org, (consulté le )

- Brian L. Stuart, « Simulating the ENIAC [Scanning our Past] », Proceedings of the IEEE, vol. 106, no 4, , p. 761–772 (ISSN 1558-2256, DOI 10.1109/JPROC.2018.2813678, lire en ligne, consulté le )

- (en) « Programming the ENIAC before its rewiring. », sur studylib.net (consulté le )

- « Vonneumann's first computer program », sur www.amphilsoc.org (consulté le )

- « ENIAC: The Army-Sponsored Revolution », sur ftp.arl.army.mil (consulté le )

- Raúl Rojas, « How to Make Zuse's Z3 a Universal Computer », IEEE Annals of the History of Computing, vol. 20, no 3, july–september 1998, p. 51–54 (DOI 10.1109/85.707574, lire en ligne [archive du ], consulté le ) (8 pages)

- (en) Mark Priestley & Thomas Haigh, « How to Make ENIAC's Accumulators Addressable Using a Subroutine », ENIAC in Action, (lire en ligne)

- (en) Aberdeen Proving Ground, Maryland, « Description and use of the Eniac Converter Code », Ballistic Research Laboratories Technical Note, , p. 14 (lire en ligne [PDF])

- (en) Thomas Haigh, « Los Alamos Bets on ENIAC: Nuclear Monte Carlo Simulations, 1947–1948 », IEEE Annals of the History of Computing, (lire en ligne [PDF])

- (en) Thomas Haigh, ENIAC in Action, The MIT Press, , 348 p. (ISBN 9780262033985), p. 164

- (en-US) « ENIAC Monte Carlo Poster | ENIAC In Action » (consulté le )

- (en) Nicholas Metropolis, « Monte Carlo Second Run Code », Library of Congress Manuscripts Division box 12, folder 5, (lire en ligne [PDF])

- (en) Mark Priestley, « Monte Carlo Second Run Code: Reconstruction and Analysis », University of Wisconsin–Milwaukee, (lire en ligne

[PDF])

[PDF]) - (en) Peter Lynch, « The ENIAC forecasts: A re-creation », Bulletin of the American Meteorological Society, (lire en ligne)

- (en) B. Jack Copeland et Giovanni Sommaruga, « The Stored-Program Universal Computer: Did Zuse Anticipate Turing and von Neumann? », dans Turing’s Revolution: The Impact of His Ideas about Computability, Springer International Publishing, (ISBN 978-3-319-22156-4, DOI 10.1007/978-3-319-22156-4_3, lire en ligne), p. 43–101

- Isaac L. Auerbach, « A static magnetic memory system for the ENIAC », Proceedings of the 1952 ACM national meeting (Pittsburgh), Association for Computing Machinery, aCM '52, , p. 213–222 (ISBN 978-1-4503-7362-3, DOI 10.1145/609784.609813, lire en ligne, consulté le )

- « Computer Memory: Past and Future », sur www.cs.umd.edu (consulté le )

- (en) Thomas Haigh, ENIAC in Action, The MIT Press, , 348 p. (ISBN 9780262033985), p. 252

- (en) Thomas Haigh, ENIAC in Action, The MIT Press, , 348 p. (ISBN 9780262033985), p. 248

- (en) Thomas Haigh, « Engineering “The Miracle of the ENIAC”: Implementing the Modern Code Paradigm », IEEE Annals of the History of Computing, , p. 11-13 (lire en ligne

[PDF])

[PDF]) - « Specifications | PDP-1 Restoration Project | Computer History Museum », sur www.computerhistory.org (consulté le )

- « 1946 Le premier ordinateur » [PDF], sur irisa.fr.

- (en) Arnold Beckmann, Costas Dimitracopoulos et Benedikt Löwe, Logic and Theory of Algorithms: 4th Conference on Computability in Europe, CiE 2008 Athens, Greece, June 15-20, 2008, Proceedings, Springer, (ISBN 978-3-540-69407-6, lire en ligne)

- (en-US) « The incredible evolution of supercomputers' powers, from 1946 to today », sur Popular Science, (consulté le )

- (en-US) Todd R. Weiss, « ENIAC at 75: Celebrating the World’s First Supercomputer », sur HPCwire, (consulté le )

- Michel Serres et Bernadette Bensaude-Vincent, Éléments d'histoire des sciences, Bordas, (ISBN 2-04-018467-8).

- Béatrice Didier, Antoinette Fouque et Mireille Calle-Gruber, Le dictionnaire universel des créatrices, Paris, Des femmes-A. Fouque, , 4982 p. (ISBN 978-2-7210-0631-8, 2721006312 et 9782721006288, OCLC 864873770, lire en ligne).

- (en-US) « ENIAC Programmers Project », sur ENIAC Programmers Project (consulté le ).

- Jan Van Der Spiegel, « ENIAC-on-a-Chip », The University of Pennsylvania, vol. 12, no 4, (lire en ligne [archive du ], consulté le )

- Jan Van Der Spiegel, « ENIAC-on-a-Chip », University of Pennsylvania, (consulté le )

- (en) « Looking Back At ENIAC: Commemorating A Half-Century Of Computers In The Reviewing System », sur The Scientist Magazine® (consulté le )

- (en) « 70 years ago, six Philly women became the world's first digital computer programmers », sur PhillyVoice, (consulté le )

Voir aussi

Articles connexes

- Liste des ordinateurs à tubes à vide

- Générateur de nombres pseudo-aléatoires, John Von Neumann a implémenté le premier générateur pseudo-aléatoire sur l'ENIAC : méthode middle-square.

- Femmes (parmi d'autres) qui ont programmé l'ENIAC :

- Jean Bartik (1924-2011), veuve de John Mauchly ;

- Betty Holberton (1917-2001) ;

- Adele Goldstine (1920-1964) ;

- Frances Spence (1922-2012).

Liens externes

- (en) « United States Patent US3120606 », description complète de l'ENIAC, 207 p.

- (en) Simulateur bas niveau de l'ENIAC

- (en) Programmation de l'ENIAC primitif (1945-1947)

- (en) Conversion de l'ENIAC en ordinateur à programme enregistré

- (en) Manuel d'utilisation original de l'ENIAC, 1946, Université de Pennsylvanie

- (en) Description du jeu d'instructions de l'ENIAC, 10 juillet 1947

- (en) Description du jeu d'instructions dans sa version de novembre 1949