x86

La famille x86 regroupe les microprocesseurs compatibles avec le jeu d'instructions de l'Intel 8086. Cette série est nommée IA-32 (pour Intel architecture 32 bits) par Intel pour ses processeurs à partir du Pentium.

| Type | |

|---|---|

| Fondation |

Un constructeur de microprocesseur pour PC doit maintenir une compatibilité descendante avec ce jeu d'instructions s'il veut que les logiciels déjà écrits fonctionnent sur les nouveaux microprocesseurs.

Origine du nom

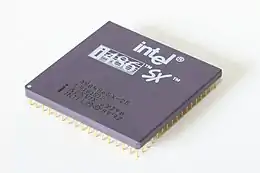

Le nom « x86 » est un terme générique pour la famille de processeurs Intel, le "x" correspondant à plusieurs valeurs, depuis le 8086, en passant par 80286, 80386 ou 80486[1].

Historique

À l'origine de conception CISC, les nouvelles générations ont été de plus en plus conçues comme des processeurs RISC, les instructions complexes étant transformées dans le microprocesseur en instructions plus élémentaires depuis le Pentium Pro.

Cette famille de processeurs, dont le Pentium est emblématique, est passée au 64 bits. La gamme AMD64 d'AMD introduit des extensions 64 bits, intégrées partiellement un an plus tard par Intel avec les instructions Intel 64 ou EM64T. Intel propose également une architecture 64 bits IA-64, différente et incompatible, pour ses processeurs Itanium et Itanium 2.

Chronologie

Le tableau ci-dessous dresse une liste non exhaustive des processeurs grand public[2] implémentant le jeu d'instructions x86, regroupés par générations qui décrivent les évolutions importantes dans l'histoire du x86.

| Génération | Introduction | Principaux modèles grand public | Espace d'adressage | Principales évolutions | |||

|---|---|---|---|---|---|---|---|

| Linéaire | Virtuelle | Physique | |||||

| x86 | 1 | 1978 | Intel 8086, Intel 8088 (1979) | 16-bit | NA | 20-bit | Premiers processeurs x86 |

| 1982 | Intel 80186, Intel 80188 NEC V20/V30(1983) | calcul rapide des adresses en hardware, opérations rapides (division, multiplication, etc.) | |||||

| 2 | Intel 80286 and clones | 30-bit | 24-bit | Mode protégé, IBM PC XT 286, IBM AT | |||

| 3 | 1985 | Intel 80386, AMD Am386 (1991) | 32-bit | 46-bit | 32-bit | Jeu d'instructions 32-bit, MMU avec pagination | |

| 4 | 1989 | Intel 80486 Cyrix Cx486S, DLC (1992) AMD Am486 (1993), Am5x86 (1995) | Pipeline de type RISC, FPU et Mémoire Cache intégrés | ||||

| 5 | 1993 | Intel Pentium, Pentium MMX (1996) | Processeur superscalaire, 64-bit bus de données, FPU plus rapide, MMX, SMP | ||||

| 1994 | NexGen Nx586 AMD 5k86/K5 (1996) | Discrete microarchitecture (µ-op translation) | |||||

| 1995 | Cyrix Cx5x86 Cyrix 6x86/MX(1997)/MII(1998) | Renommage de registres, exécution spéculative, Exécution dans le désordre | |||||

| 6 | 1995 | Intel Pentium Pro | 36-bit (EAP) | Traduction des micro-instructions, exécution spéculative, EAP (Pentium Pro), cache L2 intégré (Pentium Pro) | |||

| 1997 | Intel Pentium II, Pentium III (1999) Celeron (1998), Xeon (1998) | Support du cache L3, 3DNow!, SSE, Socket 370 | |||||

| 1997 | AMD K6/K6-2 (1998)/K6-III (1999) | 32-bit | 3DNow!, support du cache L3 (K6-III) | ||||

| Optimisation de la plateforme | 1999 | AMD Athlon, Athlon XP/MP (2001) Duron (2000), Sempron (2004) | 36-bit | FPU superscalaire, meilleure conception (jusqu'à 3 instructions x86 par top d'horloge), Slot A ou Socket A | |||

| 2000 | Crusoe | 32-bit | Very long instruction word | ||||

| Intel Pentium 4 | 36-bit | Pipeline profond, haute fréquence, SSE2, Hyper-Threading, Socket 478 | |||||

| 2003 | Intel Pentium M Intel Core (2006), Pentium Dual-Core (2007) | Optimisé pour une faible consommation d'énergie, NX Bit (Dothan) (Intel Core "Yonah") | |||||

| Efficeon | Very long instruction word, NX bit, Hyper Transport, AMD64 | ||||||

| IA-64 | Transition 64-bit 1999 ~ 2005 | 2001 | Intel Itanium (2001 ~ 2017) | 52-bit | Architecture EPIC | ||

| x86-64 | Extension 64-bit depuis 2001 | x86-64 est l'architecture étendue 64 bits, elle préserve l'intégralité de l'architecture x86. Elle réside en mode 64 bits, manque de mode d'accès dans la segmentation, présente un espace d'adressage linéaire à autorisation architecturale de 64 bits, une architecture IA-32 adaptée dans le mode de compatibilité avec le mode 64 bits est fournie pour prendre en charge la plupart des applications x86. | |||||

| 2003 | Athlon 64/FX/X2 (2005), Opteron Sempron (2004)/X2 (2008) AMD Turion (2005)/X2 (2006) | 40-bit | Jeu d'instructions x86-64, contrôleur mémoire intégré, HyperTransport, Socket 754/939/940 ou AM2 | ||||

| 2004 | Pentium 4 (Prescott) Celeron D, Pentium D (2005) | 36-bit | Pipeline très profond, très haute fréquence, SSE3, LGA 775 | ||||

| 2006 | Intel Core 2 Pentium Dual-Core (2007) Celeron Dual-Core (2008) | Faible consommation d'énergie, multi-cœur, fréquence d'horloge plus faible, SSSE3 (Penryn) | |||||

| 2007 | AMD Phenom/II (2008) Athlon II (2009), Turion II (2009) | 48-bit | quad-core monolithique, FPU 128-bit, SSE4a, HyperTransport 3, conception modulaire, Socket AM2+ ou AM3 | ||||

| 2008 | Intel Core 2 (45 nm) | 40-bit | SSE4.1 | ||||

| Intel Atom | Très faible consommation d'énergie | ||||||

| Intel Core i7 Core i5 (2009), Core i3 (2010) | out-of-order, superscalaire, bus QPI, conception modulaire, contrôleur mémoire intégré, 3 niveau de cache | ||||||

| VIA Nano | out-of-order, superscalaire, chiffrement matériel, très faible consommation d'énergie, gestion de l'énergie adaptative | ||||||

| 2010 | AMD FX | 48-bit | Huit cœurs, Multiply-accumulate, OpenCL, Socket AM3+ | ||||

| 2011 | AMD APU A and E Series (Llano) | 40-bit | PCI Express 2.0, Socket FM1 | ||||

| AMD APU C, E and Z Series (Bobcat) | 36-bit | Faible consommation énergétique | |||||

| Intel Core i3, Core i5 and Core i7 (Sandy Bridge/Ivy Bridge) | Connexion en anneau interne, cache de micro-operation décodé, LGA 1155 | ||||||

| 2012 | AMD APU A Series (Bulldozer, Trinity et suivants) | 48-bit | AVX, conception hautement modulaire, Socket FM2 ou Socket FM2+ | ||||

| Intel Xeon Phi (Knights Corner) | Coprocesseur de carte d'extension PCI-E pour système basé sur XEON, Manycore Chip, In-order P54C, VPU très large (512-bit SSE), LRBni instructions (8× 64-bit) | ||||||

| 2013 | AMD Jaguar (Athlon, Sempron) | SoC, console de jeu et processeur de périphérique intelligent basse consommation | |||||

| Intel Silvermont (Atom, Celeron, Pentium) | 36-bit | SoC, basse/très basse consommation énergétique | |||||

| Intel Core i3, Core i5 and Core i7 (Haswell/Broadwell) | 39-bit | AVX2, extensions de synchronisation transactionnelle, LGA 1150 | |||||

| 2015 | Intel Broadwell-U (Intel Core i3, Core i5, Core i7, Core M, Pentium, Celeron) | SoC, on-chip Broadwell-U PCH-LP | |||||

| 2015-2020 | Intel Skylake/Kaby Lake/Cannon Lake/Coffee Lake/Rocket Lake (Intel Pentium/Celeron Gold, Core i3, Core i5, Core i7, Core i9) | 46-bit | AVX-512 (limité à Cannon Lake-U et aux variants bureaux/serveurs de Skylake) | ||||

| 2016 | Intel Xeon Phi (Knights Landing) | 48-bit | Processeur et coprocesseur multi-coeurs pour les systèmes Xeon | ||||

| 2016 | AMD Bristol Ridge (AMD (Pro) A6/A8/A10/A12) | Integrated FCH on die, SoC, Socket AM4 | |||||

| 2017 | AMD Ryzen/Epyc | AMD's implementation of SMT, on-chip multiple dies | |||||

| 2017 | Zhaoxin WuDaoKou (KX-5000, KH-20000) | Introduction de la toute nouvelle architecture x86-64 de l'entreprise chinoise | |||||

| 2018-2021 | Intel Sunny Cove (Ice Lake-U and Y), Cypress Cove (Rocket Lake) | 57-bit | Première implémentation du jeu d'instructions AVX-512 dans le grand public. Ajout du Vector Neural Network Instructions (VNNI) | ||||

| 2020 | Intel Willow Cove (Tiger Lake-Y/U/H) | Dual ring interconnect architecture, mise à jour du Gaussian Neural Accelerator (GNA2), nouvelles instructions AVX-512 (Vector Intersection), protection contre les malwares au niveau processeur avec Control-Flow Enforcement Technology (CET) | |||||

| 2021 | Intel Alder Lake | Architecture hybride avec cœurs haute performances (Golden Cove) et cœurs basse consommation (Gracemont), support du PCIe 5.0 et DDR5, mise à jour du Gaussian Neural Accelerator (GNA3) | |||||

| Génération | Introduction | Principaux modèles grand public | Espace d'adressage | Principales évolutions | |||

Architecture

La conception de la gamme x86 a mis l'accent sur la compatibilité ascendante. Ainsi, les générations successives de processeurs admettent plusieurs modes de fonctionnement, qui diffèrent en particulier du point de vue de l'accès à la mémoire.

Les logiciels pensés en 32 bits (i386) fonctionnent donc sur une architecture 64 bits (AMD64).

Accès mémoire

Les possibilités d'adressage mémoire de la gamme x86 remontent au 8080, qui avait 16 bits de bus d'adresse et pouvait donc accéder à 64 Ko de mémoire.

Le 8086, pour faciliter le passage du 8080 au 8086, introduit l'adressage segmenté, où l'adresse référencée par segment:offset est segment · 0x10 + offset, avec segment et offset tous deux sur 16 bits. Cela fournit 1 Mo de mémoire adressable, divisée en segments de 64 Ko, un segment commençant tous les 16 octets. Le processeur a 4 registres de segment : un pour le code, un pour les données, un pour la pile et un supplémentaire (qui sert entre autres de destination dans les instructions de copie de chaînes de caractères). Intel introduit des « modèles mémoire ». Dans le modèle tiny, qui imite le modèle mémoire du 8080, tous les registres de segments ont la même valeur et on accède donc effectivement à 64 Ko de mémoire. C'est le modèle utilisé sous DOS, par les exécutables .com. Dans le modèle small, les registres ont des valeurs différentes mais ne changent pas : on a donc 64 Ko pour le code, 64 Ko pour les données, 64 Ko pour la pile. Pour manipuler plus de mémoire, il faut faire des accès « far », c'est-à-dire aller chercher le mot en mémoire en changeant d'abord la valeur du registre de segment, puis en lisant le segment à l'offset voulu. Le modèle « large » fait des accès far dans le code et les données et donc utilise effectivement le mébioctet d'espace adressable. Les modèles medium (64 Ko de données, plusieurs segments de code) et compact (plusieurs segments de données, 64 Ko de code) sont des compromis.

Le 80286 brise la barrière des 1 024 Ko en introduisant le mode protégé : les segments ne se réfèrent plus à l'adresse segment·0x10 mais à une table (la GDT ou la LDT) qui maintient en plus les informations de protection. L'espace adressable est de 16 Mo, l'espace virtuel est potentiellement de 1 Go, un segment ne peut pas dépasser 64 Ko. Avec le 80386, Intel introduit un processeur 32 bits. Les segments peuvent être aussi gros que tout l'espace adressable, soit 4 Go. La pagination vient s'ajouter à la segmentation.

Notes et références

- (en) https://techterms.com/definition/x86

- (en) « Microprocessor Hall of Fame », Intel (consulté le ).