Silicium sur isolant

Le silicium sur isolant (en anglais : SOI ou Silicon On Insulator) est une structure constituée d'un empilement d'une couche de silicium (de 50 nm à quelques µm d'épaisseur) sur une couche d'isolant. Cet isolant peut être du saphir (Silicon-On-Sapphire), de l'air (Silicon-On-Nothing) ou du dioxyde de silicium (SiO2).

Cette technologie est une alternative prometteuse au silicium brut dans la réalisation de transistors opérant à de hautes fréquences[1]. En effet, malgré son coût de développement supérieur de 10 % par rapport aux technologies classiques sur substrat massif, le gain en performance est évalué entre 20 et 35 %. Les fréquences de coupure sont supérieures à 150 GHz pour la technologie 130 nm. Avec l'utilisation de substrats fortement résistifs, les pertes sont diminuées et les performances accrues notamment au niveau du bruit micro-onde. Ainsi, les performances fréquentielles des dispositifs fabriqués sur des technologies silicium sont à revoir à la hausse. Il est généralement admis que la technologie SOI permet de gagner une génération de puce.

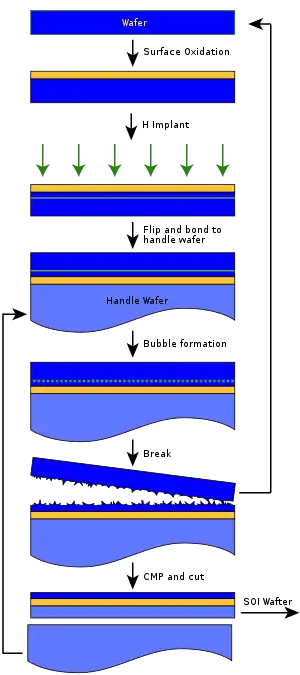

La technologie SOI compte plusieurs procédés industriels qui ont été développés pour réaliser un film de silicium sur une couche isolante[2] - [3] - [4]. Le plus ancien est le SOS ou Silicon-On-Sapphire. Depuis les années 1980, d'autres techniques ont été mises au point et sont devenues des standards industriels. Les deux principaux procédés sont le SIMOX[5] et le BSOI. dont une technique dérivée est la technologie Smart Cut[6] de la société Soitec. Ces dernières techniques de fabrication dominent actuellement le marché du SOI, notamment la technique Smart Cut qui représente environ 90 % de la production actuelle de SOI.

Principe

L'approche SOI consiste à interposer une fine couche isolante d’oxyde de silicium entre l’épi-couche et le substrat en silicium.

Pour faire germer l’épi-couche, on a recours à l’épitaxie (i.e. le procédé permettant aux atomes se déposant de se placer correctement, donc de s’organiser dans un monocristal continu et sans défauts aux interfaces).

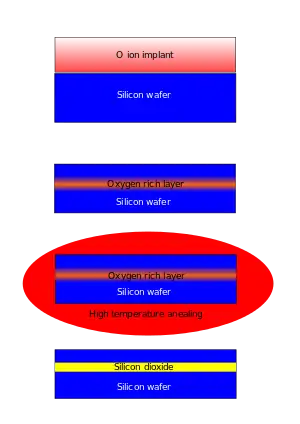

La mise en œuvre est délicate car il faut respecter la continuité du substrat de silicium. L’idée consiste à faire naître l’isolant à l’intérieur du silicium par une technique dénommée SIMOX (ou Separation by IMplantation of Oxygen, une injection à très haute température d’oxygène purifié)[7].

Historique

- 1963 : Synthèse du SiO2 par implantation d'oxygène ;

- 1964 : Début de la technologie SOS ;

- 1976/1978 : HP/Toshiba lance des micro-processeurs 16-bit en CMOS SOS ;

- 1978 : Naissance du procédé SIMOX mis au point par Izumi au NTT ;

- 1982 : Première mémoire SRAM de 1kB créé chez NTT ;

- 1987 : HP réalise des circuits CMOS SOI complètement déplété ;

- 1988 :

- Circuits CMOS complètement déplétés à 2 GHz de Hewlett-Packard ;

- Le LETI crée un microprocesseur 16-bit en SIMOX ;

- 1989 : AT&T réalise un circuit CMOS complètement déplété à 6,2 GHz ;

- 1991 :

- MOSFET SOI de 14 GHz de fT réalisé par Westinghouse ;

- Naissance du procédé Smart Cut mis au point par Michel Bruel au LETI (Laboratoire d'Électronique de Technologie de l'Information) ;

- 1993 : MOSFET SOI de 23 GHz de fT réalisé par Westinghouse ;

- 1994 : Le LETI crée un microprocesseur 32-bit en SIMOX. Technologie 0,35 µm ;

- 1997 : Technologie 250 nm. PowerPC 32-bit créé en Technologie 0,25 µm par IBM ;

- 1998 : PowerPC 64-bit créé par IBM ;

- 2001 : Technologie 120 nm. fT et fmax ~150 GHz pour un nFET SOI avec Lg effective ~70 nm ;

- 2002 : Transistor le plus petit du monde créé par IBM. Lg~6 nm et tsi~6 nm ;

- 2003 : Technologie 90 nm. Alliance IBM et AMD pour la création de dispositifs en technologie 65 nm pour 2005.

- 2004 : SOITEC et ASM produisent des tranches de SOI de 300 mm de diamètre[8]. Commercialisation par AMD de processeur 64 bit Opteron et Athlon en technologie 130 nm et 90 nm ;

- 2005 : Technologie 65 nm en développement.

Les acteurs

Les principaux acteurs dans le domaine des substrats SOI sont donnés ci-dessous. Pour les principales industries, la marque du produit et/ou le diamètre maximal de la tranche sont indiqués entre parenthèses. Pour plus d'informations, le lecteur pourra se référer aux sites internet de ces fondeurs.

- SOS : Peregrine (UTSi), Kyocera, Union Carbide, Asahi kasei ;

- ZMR : Mitsubishi ;

- SIMOX : IBIS (Advantox MLD-UT, 300 mm), SUMCO (200 mm), IBM (300 mm), NSC, Komatsu ;

- BSOI : Soitec (Unibond, 300 mm), Canon (Eltran, 300 mm), SiGen (Nanocleave, 300 mm), Shin-Etsu Handotai (Unibond, 300 mm), Ultrasil Corporation (200 mm), Sumco (150 mm), Isonics (200 mm), OKMETIC (200 mm), BCO, Hughes, SiBond.

L'entreprise française Soitec possède actuellement environ 80 % du marché mondial du SOI. Un marché qui est actuellement en pleine expansion.

Liens

Notes et références

- (en) G. K. Celler et S. Cristoloveanu, « Frontiers of silicon-on-insulator », J Appl Phys, vol. 93, no 9, , p. 4955 (DOI 10.1063/1.1558223, lire en ligne)

- United States Patent 6,835,633 SOI wafers with 30-100 Ang. Buried OX created by wafer bonding using 30-100 Ang. thin oxide as bonding layer

- United States Patent 7,002,214 Ultra-thin body super-steep retrograde well (SSRW) FET devices

- Ultrathin-body SOI MOSFET for deep-sub-tenth micron era; Yang-Kyu Choi; Asano, K.; Lindert, N.; Subramanian, V.; Tsu-Jae King; Bokor, J.; Chenming Hu; Electron Device Letters, IEEE; Volume 21, Issue 5, May 2000 Page(s):254 - 255

- Jean Sébastien Danel, Micro Usinage Des Materiaux Monocristallins, p.8

- https://www.soitec.com/en/products/smart-cut

- Nano-informatique et Intelligence Ambiante, Jean-Baptiste Waldner, Hermes Science, London, 2006, (ISBN 2746215160), p126-p127

- VIPpress.net Soitec lance la production en volume de tranches RF-SOI en 300 mm, (19/02/2016)