Transistor à effet tunnel

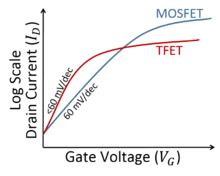

Le transistor à effet tunnel (TFET) est un type de transistor encore expérimental. Même si sa structure est proche de celle d'un transistor à effet de champ métal-oxyde-semiconducteur (MOSFET), les mécanismes fondamentaux de commutation diffèrent faisant de ce dispositif un candidat prometteur pour l'électronique faible puissance. Les TFET commutent en modulant l'effet tunnel à travers une barrière au lieu de moduler l'émission thermoïonique au dessus d'une barrière, comme dans le traditionnel MOSFET. De ce fait, les TFET ne sont pas limités par le transport statistique de Maxwell–Boltzmann des porteurs, ce qui limite le courant de drain des MOSFET à une pente de sous-saturation d'environ 60 mV/décade de courant à la température ambiante (exactement 63 mV par décade à 300 K[1]).

Le concept a été proposé par Chang et al, chez IBM [2]. Joerg Appenzeller et ses collègues d'IBM ont été les premiers à démontrer qu'une variation inférieure à celle de 60 mV/dec du MOSFET est possible. En 2004, ils ont annoncé qu'ils avaient créé un transistor à effet tunnel à base de nanotube de carbone manifestant seulement 40 mV par décade[3].

Des travaux théoriques indiquent une économie d'énergie significative en utilisant des TFET à basse tension dans des circuits logiques à la place des MOSFET[4].

Dans les dispositifs à base de MOSFET la pente de 63 mV/dec de courant est une limite fondamentale à l'économie d’énergie. Le ratio entre le courant ON et le courant OFF (en particulier le courant de fuite) est donné par le ratio entre la tension de Seuil et la pente de sous-saturation.

La pente de sous-saturation est proportionnelle à la vitesse du transistor. Plus faible est la pente (en mV/dec), plus le transistor est rapide. Pour une vitesse et un courant de fuite donnés, la pente de sous-saturation détermine une tension minimale d'activation. Depuis 2003, les développements technologiques sont presque bloqués dans la réduction de tension de seuil ce qui les empêche alors de réduire la tension d'alimentation des dispositifs (qui pour des raisons techniques est au moins 3 fois la tension de seuil pour des applications de haute performance). Par conséquent, la vitesse des processeurs ne s'est pas développée aussi rapidement qu'avant 2003 (voir CMOS). L'avènement d'une version de TFET compatible avec la production de masse et avec une pente bien en dessous de 63 mV/dec doit permettre à l'industrie de continuer sur la tendance de miniaturisation vérifiée depuis les années 90 où la fréquence des processeurs doublait tous les 3 ans (voir loi de Moore).

Structure

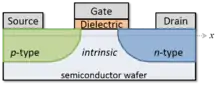

La structure de base d'un TFET est proche de celle d'un MOSFET à la différence près que la source et le drain du TFET sont dopés de types opposés (voir la figure). Une structure courante de TFET est une jonction P-I-N (dopé-P, intrinsèque, dopé-N). Le potentiel électrostatique de la jonction intrinsèque est contrôle par la grille.

Fonctionnement

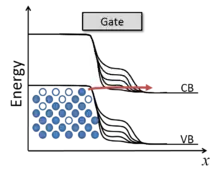

Le dispositif est contrôlé par la polarisation de la grille accumulant des électrons dans la région intrinsèque. A polarisation suffisante, un effet tunnel bande à bande a lieu lorsque la bande de conduction de la région intrinsèque est au même niveau d’énergie que la bande de valence de la région P. Les électrons de la bande de valence de la région P sautent par effet tunnel dans la bande de conduction de la région intrinsèque et un courant peut alors circuler à travers le dispositif.

Prototypes

Un groupe IBM ont été les premiers à démontrer que des pentes inférieures aux 60 mV par décade du MOSFET étaient possibles. En 2004, ils ont réalisé un transistor à effet tunnel avec un nanotube de carbone en guise de canal et une pente de sous-saturation de 40 mV par décade[5].

En 2010, de nombreux TFET ont été fabriqués dans des matériaux différents, mais aucun n'a encore été en mesure de montrer une pente de sous-saturation assez raide aux courants requis pour l'utilisation dans l’électronique grand public.

Travaux futurs

Des structures à double-grille ont été proposées pour répondre aux défis comme des profils de dopages très contrastés, associés à la structure latérale du TFET. Cependant, ce type de dispositifs est potentiellement rendu inutilisable par des fuites de grilles causées par de grands champs verticaux dans la structure de l'appareil[6].

Théorie et simulations

Des simulations en 2013 ont montré que des TFET à base de l'InAs-GaSb peuvent avoir une pente de sous-saturation de 33 mV/décade dans des conditions idéales[7].

Références

- DeMicheli, G.; Leblebici, Y:;Gijs, M.; Vörös, J. (2009). "Nanosystems Design and Technology." Springer. doi:10.1007/978-1-4419-0255-9

- Chang, L. L., and L. Esaki. "Tunnel triode—a tunneling base transistor." Applied Physics Letters 31.10 (1977): 687-689

- J. Appenzeller, « Band-to-Band Tunneling in Carbon Nanotube Field-Effect Transistors », Physical Review Letters, vol. 93, no 19, (DOI 10.1103/PhysRevLett.93.196805, lire en ligne)

- A. C. Seabaugh et Q. Zhang, « Low-Voltage Tunnel Transistors for Beyond CMOS Logic », Proceedings of the IEEE, vol. 98, no 12, , p. 2095–2110 (DOI 10.1109/JPROC.2010.2070470)

- « The Tunneling Transistor »

- J. T. Teherani, S. Agarwal, E. Yablonovitch, J. L. Hoyt et D. A. Antoniadis, « Impact of Quantization Energy and Gate Leakage in Bilayer Tunneling Transistors », IEEE Electron Device Letters, vol. 34, no 2, , p. 298 (DOI 10.1109/LED.2012.2229458)

- Device Simulation of Tunnel Field Effect Transistor (TFET). Huang 2013