Intel 4004

Le 4004 d'Intel est le premier microprocesseur commercialisé, c'est-à-dire la première intégration réussie d'une grande partie des fonctions d'un processeur sur un seul et unique circuit intégré.

| Fréquence | 740-750 kHz |

|---|---|

| Largeur bus données | 4 bits |

| Largeur bus adresse | 12 bits (multiplexé) |

Il est d'abord produit en exclusivité pour l'industriel qui a commandité son développement, Busicom, en . Après avoir fait lever la clause d'exclusivité, Intel annonce sa commercialisation le [1] - [2].

Sa réalisation est rendue possible par la toute nouvelle technologie des self-aligned gates, qui permet à son concepteur, Federico Faggin, d'intégrer sur un même circuit intégré 2 300 transistors.

Avec une puissance d'exécution de 92 600 opérations par seconde à une fréquence maximale de 740 kHz[3], il est d'une puissance comparable à l'ENIAC, le premier ordinateur moderne dévoilé en 1946, qui occupait 167 m2 pour un poids total de 30 t.

Le 4004 reste nettement moins performant que les processeurs des mini-ordinateurs de la même époque. Par contre, il permet d'imaginer de construire des ordinateurs nettement moins chers que ceux‑ci : des micro-ordinateurs. Le 4004 et les puces de support qu'il utilise sont ainsi commercialisés par Intel en tant que « Micro Computer Set » (« Ensemble pour Micro-ordinateur ») MCS-4.

Le 4004 et le chipset MCS‑4 ont cependant de nombreuses limitations qui font qu'ils ne seront pas utilisés pour construire des microordinateurs mais plutôt des contrôleurs embarqués.

Le 4004 est par contre suivi l'année suivante par le premier microprocesseur 8 bits, le 8008 (et par le 4040, un 4004 révisé), puis en 1974 par le microprocesseur qui commence effectivement la révolution des micro-ordinateurs, le 8080.

Concepteurs

Le 4004 a été conçu par deux ingénieurs d'Intel : Marcian Hoff, qui mit son architecture au point en 1969, et Federico Faggin, l'unique designer de puce du projet MCS-4. Faggin avait une expérience de la conception de transistor MOSFET sur silicium, et notamment de la nouvelle technique dite de « self-aligned gates », qu'il avait mise au point à Fairchild Semiconductor en 1968. Ce dernier a dirigé avec succès le projet MCS-4 en 1970-1971.

Au moment de l’invention du microprocesseur, les ingénieurs savaient concevoir l'architecture d'un microprocesseur et en définir la logique, mais personne n’était encore en mesure d'en réaliser un sur une puce unique de silicium[4].

Historique

En 1969, la société japonaise Busicom, premier gros client d'Intel (fondé la même année, en 1968) se rapprocha d'Intel afin de discuter du développement de circuits intégrés dont elle avait conçu l'architecture logique. Ceux-ci leur étaient nécessaires pour réaliser un type de calculatrices. L'architecture utilisée par Busicom était répartie en sept puces : un CPU à but spécifique lui-même divisé en trois puces avec une mémoire en lecture seule (ROM) destinée au stockage des programmes ; un registre à décalage ayant pour but de stocker l'information; et deux puces d'entrée et sortie (I/O).

Marcian Hoff (surnommé Ted Hoff), assisté par Stan Mazor (en) d'Intel, proposa une architecture plus simple employant quatre puces : une architecture de CPU d'utilité générale utilisant la mémoire vive pour stocker l'information qui pouvait potentiellement être intégrée dans une puce, une puce de mémoire en lecture seule (ROM), une puce de mémoire à accès aléatoire (RAM) et une puce entrée et sortie (I/O). Les ingénieurs de Busicom évaluèrent la proposition de Hoff et l'acceptèrent en .

Federico Faggin, qui était alors employé chez Fairchild Semiconductor, fut engagé chez Intel en pour y diriger le projet et réaliser le 4004. Durant son passage chez Fairchild, Faggin créa en 1968 la technologie originale du silicon gate avec grille auto-alignée (« self-aligned gate »), appelée « Silicon Gate Technology (SGT) », une technologie qui permit de réaliser le microprocesseur, et réalisa le premier circuit intégré MOS du monde utilisant la SGT (le Fairchild 3708), prouvant la viabilité de la nouvelle technologie. Alors qu'il travaillait chez Olivetti à Borgolombardo en Italie en 1961, Faggin avait acquis l'expérience sur la conception et la réalisation d'un petit ordinateur électronique et était très familier avec son architecture. À Intel, Federico Faggin créa une nouvelle méthodologie de projet, inexistante jusque-là, employant la technologie SGT pour la logique du processeur, qui permit d'intégrer le microprocesseur dans une seule puce. Il fut impliqué aussi dans tous les aspects du développement avec l'assistance de Masatoshi Shima de Busicom. Shima, par la suite, écrivit le logiciel pour la calculatrice imprimante de bureau pour Busicom, le premier produit final à utiliser le microprocesseur.

Étant donné que Busicom avait les droits exclusifs sur le 4004, Intel ne pouvait le vendre à aucun autre client. Faggin, voyant le potentiel que le 4004 pouvait avoir sur des applications générales, exhorta la direction d'Intel à renégocier le contrat avec Busicom pour permettre d'élargir le marché du microprocesseur. Ed Gelbach, issu de la société Texas Instruments, qui venait juste d'être nommé vice-président de la section marketing et ventes d'Intel, comprit rapidement le potentiel du microprocesseur et décida de le commercialiser. Le 4004 fut enfin introduit sur le marché général en , ouvrant ainsi un nouveau chapitre dans l'histoire de la microélectronique.

Prédécesseur

Bien que le 4004 soit largement considéré comme le premier microprocesseur, un autre modèle a été développé un an avant en 1970 par Ray Holt de la société américaine Central Air Data Computer pour équiper l'avion de chasse F-14 Tomcat de l'avionneur Grumman. Toutefois, l'unité centrale de traitement (CPU) de Holt, ainsi que les autres CPU antérieurs à 1970, était composée d'au moins trois puces (chips) LSI et n'était donc pas intégrée dans un chip unique : il ne s'agissait pas d'un microprocesseur. L'existence de ce modèle beaucoup plus performant que le 4004 est révélée en 1998[5].

Caractéristiques techniques

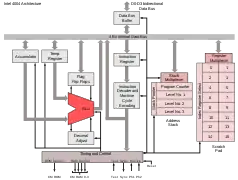

Architecture du microprocesseur Intel 4004.

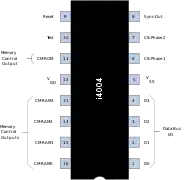

Architecture du microprocesseur Intel 4004. Brochage du microprocesseur Intel 4004.

Brochage du microprocesseur Intel 4004..jpg.webp) Deux processeurs C4004 dont un ouvert.

Deux processeurs C4004 dont un ouvert.

Les 4004 sont sortis dans un boîtier DIP à seize broches en céramique le . C'est la première fois que toutes les fonctions d'un processeur sont réunies sur un seul et unique circuit intégré, ce qui en fait le premier microprocesseur de l'histoire et de l'industrie. Le tarif industriel à sa sortie est de deux cents dollars.

Les dimensions du circuit intégré sont de 3,81 mm de long sur 2,79 mm de large, soit environ 10,63 mm2. Il offre ainsi des performances équivalentes aux 66 m3 de l'ENIAC concentrées sur seulement 10 mm2.

Il comporte 2 300 transistors pMOS (Metal-Oxide Semiconductor à canal P) en technologie 10 µm, alimentés en −15 V.

Conçu pour du calcul décimal codé binaire, il a une architecture de traitement 4 bits, c'est-à-dire qu'il manipule des « caractères » de 4 bits (des quartets), suffisant pour représenter des chiffres entre 0 et 9.

Le 4004 dispose d'une unité arithmétique et logique (UAL), d'un accumulateur et de seize registres de données, tous sur 4 bits. L'UAL permet d'effectuer quelques calculs simples : incrémentation et décrémentation, addition et soustraction, décalages, ajustement décimal et propagation de la retenue.

L'adressage, la taille des mots et le stockage sont complètement différents pour le programme et pour les données :

- le programme est constitué de mots de 8 bits (des octets) et doit être stocké dans une mémoire ROM séparée. L'adressage est sur 12 bits, soit un espace d'adressage de 4 096 octets d'instructions machines ;

- les données sont constituées de mots de 4 bits (des quartets) stockées en mémoire vive. L'adressage suit un schéma segmenté sur 8 bits qui permet d'adresser 1 280 quartets (4 « lignes » de mémoire vive, avec 256 quartets de « mémoire principale » et 64 quartets de « statut » par ligne).

En raison du petit nombre de broches, le bus de données et le bus d'adresse ne sont pas séparés mais sont multiplexés sur un unique bus externe à 4 bits.

L'architecture externe est intermédiaire entre une architecture Harvard et une architecture de von Neumann :

- comme une architecture Harvard, le programme et les données ont un stockage séparé, permettant d'avoir des adressages et des tailles de mots différents ;

- contrairement aux architectures Harvard dites pures, l'utilisation d'un bus commun pour les transferts interdit l'accès simultané au programme et aux données.

Outre un compteur ordinal, le 4004 intègre également une pile d'exécution interne profonde de trois niveaux.

Le jeu d'instructions comporte 46 instructions machines, dont 41 instructions sur 1 octet et 5 instructions sur 2 octets.

Le 4004 est cadencé par une horloge externe à 740 kHz. Chaque instruction nécessite un cycle d'instruction d'une durée fixe de huit cycles d'horloge (ou éventuellement seize cycles pour les instructions sur 2 octets) :

- les trois premiers cycles servent à envoyer à la mémoire ROM une adresse sur 12 bits ;

- les deux cycles suivants servent à lire depuis la ROM l'instruction sur 1 octet à cette adresse ;

- les trois derniers cycles sont alors utilisés pour décoder et exécuter cette instruction.

Pour une horloge externe à 740 kHz, chaque cycle d'instruction dure 10,8 μs, ce qui permet au 4004 d'effectuer jusqu'à 92 600 instructions par seconde.

Famille de composants complémentaires

Le 4004 est fourni avec une famille de composants d'appui compatibles avec son fonctionnement : synchronisation sur le cycle d'instruction, multiplexage du bus, adressage segmenté de la mémoire vive, etc. L'ensemble du 4001 et de ces composants d'appui est commercialisé sous le nom de « MCS-4 » :

- 4001 : mémoire morte de 256 octets (programme de 256 instructions de 8 bits), et port intégré d'entrée/sortie sur 4 bits ;

- 4002 : mémoire vive de 80 mots de 4 bits, et port intégré d'entrée/sortie sur 4 bits. La partie mémoire de la puce est organisée en quatre registres de vingt mots de 4 bits :

- 16 mots de données (utilisés pour les chiffres de la mantisse dans la calculatrice d'origine),

- 4 mots de statut (utilisés pour les exposants et les signes dans la calculatrice d'origine) ;

- 4003 : sortie registre à décalage de 10 bits pour scanner les claviers, affichages, imprimantes, etc.

À peu près un an et demi après l'avènement du MCS-4, son concepteur (designer) Federico Faggin, ajouta les chips 4008 et 4009 pour permettre la connexion directe du 4004 aux mémoires standard, augmentant ainsi le nombre de composantes mémorielles qui pouvaient être utilisées ;

- 4008 : adresse verrouillée de 8 bits pour l'accès aux puces de mémoires standards, et port intégré d'entrée/sortie sur 4 bits ;

- 4009 : convertisseur d'entrée/sortie et de programmes pour les mémoires standards et les puces d'entrées/sorties.

Note : dans la série MCS-4 originale, le 4004 ne nécessitait pas les chips optionnels 4008/4009 pour fonctionner en tant que système parce qu'il se connectait directement avec jusqu'à seize 4001 (mémoire morte) et seize 4002 (mémoire vive).

Objet de collection

L'Intel 4004 est naturellement une des puces collectionnées les plus recherchées au monde. Les 4004 de très grande valeur sont ceux qui sont en or et blanc, avec ce qu'on appelle « des traces grises » sur la partie blanche. En 2007, de telles puces ont atteint environ 1 500 $ sur eBay. Celles en blanc et or sans traces grises sont de valeurs légèrement inférieures et atteignent typiquement 600 à 800 $. Les puces sans « code de date » en dessous, sont des versions plus anciennes, et valent légèrement plus, de l'ordre de 1 200 $. À noter d'autres puces de valeur telles que les Intel 4040.

Notes et références

- « Le premier micro-processeur commercialisé », sur ACONIT (consulté le ).

- « Le premier microprocesseur: le 4004 d'Intel », sur Histoire de l'informatique (consulté le ).

- (en) « Intel MCS-4 datasheet » [PDF], sur chipdb (consulté le ).

- (en) « The Crucial Role Of Silicon Design In The Invention Of The Microprocessor », sur intel4004 (consulté le ).

- Yohan Demeure, « Le premier microprocesseur de l’histoire est celui d’un avion de chasse de l’US Navy », Sciencepost, (lire en ligne).

Voir aussi

Liens externes

- (en) Schéma du 4004, sur 4004.com.

- (en) Un assembleur en ligne pour Intel 4004.

- Initiales F.F. sur le 4004. Le 4004 est signé avec les initiales « F.F. » de son concepteur, Federico Faggin. La signature de la puce a été un geste spontané de fierté pour sa réalisation, et aussi une idée originale ensuite imitée par de nombreux ingénieurs chez Intel.

- Couverture du programme et résumé de la communication de Faggin à la conférence IEDM de 1968. C'est à la conférence IEDM (International Electron Devices Meeting) de 1968 qu'est présentée la technologie Silicon Gate avec « grilles auto-alignées », qui rendra possible la réalisation du 4004.

- La couverture de la revue Electronics (29 septembre 1969) montre le Fairchild 3708, le premier circuit intégré MOS commercial du monde à utiliser la technologie Silicon Gate.

- Trente-cinquième anniversaire du Intel 4004. Présentations en direct sur le 4004 par Ted Hoff et Federico Faggin enregistrées par YouTube.

- Prototype d'ingénierie de la calculatrice Busicom (don de Federico Faggin au Computer History Museum, Mountain View, California). C'est pour cette calculatrice de bureau, la Busicom 141-PF, que le 4004 fut originellement développé. Ce prototype unique a été offert à Federico Faggin par le président de Busicom, Yoshio Kojima, en reconnaissance de son succès dans la conception et le développement du chipset MCS-4. Après l'avoir conservé chez lui pendant 25 ans, Faggin l’a donné au CHM en 1996.

- Federico Faggin, The MOS Silicon Gate Technology and the First Microprocessors, The Journal of the Nuovo Cimento, Italian Physical Society, vol. 38, no 12, 2015 (version de prépublication).