Mémoire mono-électronique

Améliorer la performance des mémoires électroniques (i.e. mémoire à semi-conducteurs), c’est réduire le nombre d’électrons nécessaires au stockage d’un bit d’information. Depuis les débuts de l’informatique cet objectif de minimiser les électrons recrutés lors d’une opération de stockage d’un bit élémentaire conditionne l’évolution des dispositifs mémoire. À ce jour, ce sont encore plusieurs centaines de milliers d’électrons qui sont nécessaires pour stocker une information binaire.

Pour inscrire un simple bit de données dans une cellule mémoire RAM, un transistor transfère près d’un demi-million d’électrons à une capacité adjacente. Cette quantité minimale de porteurs électriques est nécessaire pour assurer la fiabilité de l’information stockée, c'est-à-dire la préserver et la rendre détectable au milieu d’un « bruit électrique » ambiant.

La densité maximale de stockage est fixée par la taille de ces petits condensateurs, dont les dimensions sont directement proportionnelles à la quantité de porteurs électriques nécessaires pour le stockage de la donnée. Un dispositif qui fonctionnerait en mobilisant moins d’électrons pour stocker une information serait donc plus petit et consommerait moins d’énergie.

Les mémoires mono-électronique ou SEM (Single Electron Memory)

Les structures d’étude ou dispositifs monoélectroniques étudiés sont des composants mettant à profit les effets quantiques et/ou de blocage de Coulomb permettant d’envisager la régulation de l’écoulement de la charge électron par électron et/ou le stockage de l’information avec un nombre fixe (i.e. non fluctuant) d’électrons.

Les potentialités d’application sont du domaine des SEM (Single Electron Memory) et des SET (Single Electron Transistor) à l'horizon 2010-2015. L’observation des effets de confinement quantique et de blocage de Coulomb a été obtenue surtout aux basses températures. Pour des applications à température ambiante, les dimensions critiques des nanodispositifs doivent se situer en deçà de 3-4 nanomètres.

L'électronique à un électron

En 1911, Millikan mesurait pour la première fois la charge de l'électron en observant la chute de gouttelettes d'huile. Aujourd'hui, on est capable de contrôler le transfert d'électrons un par un dans des dispositifs submicroniques.

Les électrons dans un métal forment un gaz dégénéré où l'extension de leur fonction d'onde est plus grande que la distance qui les sépare : ils sont en quelque sorte fondus les uns dans les autres. Pour cette raison, le caractère discontinu du courant électrique est masqué dans un métal et même dans un semi-conducteur.

Le contrôle du passage des électrons un par un est néanmoins possible en combinant deux phénomènes : le franchissement d'une barrière de potentiel par effet tunnel et la répulsion coulombienne entre électrons.

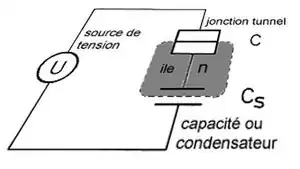

Le circuit élémentaire, appelé "boîte à électrons", permettant de contrôler leur passage est représenté sur la figure 1. Ce circuit se compose d'une jonction tunnel reliée à une capacité Cs

Le rôle de la jonction tunnel est de permettre la séparation d'un électron du reste du gaz électronique du métal, les électrons passant un à un à travers la barrière isolante. La partie comprise entre les deux capacités s'appelle une île. Sa charge q est proportionnelle au nombre n d'électrons ayant franchi la barrière tunnel : q = ne.

La tension U, appliquée aux bornes du circuit, va déterminer la charge de l'île. On peut alors définir deux régimes :

- À haute température, l'énergie d'un électron sur l'île (E=e2/2(Cs+C)) est petite devant l'énergie des fluctuations thermiques kBT. Les électrons entrent et sortent facilement de l'île dont la charge moyenne <n>e est alors donnée par CsU.

- À très basse température, c'est-à-dire lorsque kBT<<E, alors <n> prend la valeur entière la plus proche de CsU/e. <n> est donc une fonction croissante (en forme d'escalier) de la tension U présente aux bornes du système.

La condition kBT<<E nécessite des capacités de l'ordre du femtofarad (c’est-à-dire 1E-15 F ) et des températures bien inférieures au kelvin.

Technologie de transition de la mémoire RAM vers la mémoire SEM

Une nouvelle génération de mémoire RAM pourrait combiner les avantages de la DRAM actuelle (densité d’intégration) et de la SRAM (non-volatilité) et améliorer radicalement les performances de ces deux technologies. À la fois mémoire vive et stockage de masse très miniaturisé dont l’impact majeur pourrait retentir sur les filières numériques les plus significatives : les dispositifs mobiles, téléphones, lecteurs enregistreur audio/video et autres PDAs…

C'est une technologie de transition vers les véritables mémoires mono-électroniques (SEM ou Single-Electron Memory) dans lesquels la présence ou l’absence d’un unique électron dans un atome permettra de matérialiser une information binaire.

Composants et technologies de l'ère post CMOS

La technologie CMOS ultime, consistera à développer de nouvelles architectures de dispositifs MOS à contrôle électrostatique renforcé afin d'aboutir à un transistor quasi-balistique.

Cela nécessitera des efforts colossaux en termes de procédés technologiques afin d'améliorer notamment les propriétés de transport par des effets de contraintes mécaniques (permettant une ingénierie de bande appropriée) et de réaliser des composants de faibles dimensions dans lesquels l’accès ne pénalise pas les performances de transport.

Les orientations majeures de la recherche dans le domaine de CMOS de l'ultime s'articulent autour des domaines suivants :

- les films minces de type SOI ;

- les transistors à effet de champ FET multigrilles combinant les effets de contrainte ;

- les diélectriques à haute permittivité réduisant les fuites de grille ;

- ainsi que l’amélioration des procédés technologiques de fabrication (lithographie, gravure …).

On considère que la fin du CMOS standard sera la génération (ou « nœud technologique ») 16 nm. Au-delà de cette dimension, d’autres technologies émergentes seront envisagées pour l’ère du post-CMOS. Ainsi, concernant les mémoires (DRAM, Mémoire Flash, MRAM,...), les grandes orientations de recherche vont vers l’amélioration des performances de stockage des mémoires flash traditionnelles par discrétisation des sites de stockage (nanocristaux, pièges, molécules,...) en remplacement de le grille flottante continue, l’utilisation d’autres concepts de stockage (changement de phase ou de résistance, ferro, magnéto,...), les mémoires à peu d’électrons (SEM, SET) ou encore à fonctionnement moléculaire. Pour les technologies logiques en rupture avec le CMOS standard, qui seront poussées à l’extrême probablement jusqu’au nœud 16nm, on envisage l’émergence d’autres alternatives plus amont. Parmi ces possibilités, on trouve les jonctions supra RSFQ, les nanotubes de carbone (CNT), les SET (single electron transistors), les dispositifs tunnel résonant (RTD), les spinFETs (transistor à transport de spin), les QCA (automates à cellules quantiques) ou encore les dispositifs moléculaires.

Bibliographie

Article extrait de Nano-informatique et Intelligence Ambiante, Jean-Baptiste Waldner, Hermes Science, London, 2006, (ISBN 2746215160), avec l'autorisation des Éditions Hermes Science.

Références

"Dans le cadre du programme européen ESPRIT Long Term Research FASEM (Fabrication and Architecture of a Single Electron Memory) nous devons montrer la faisabilité de réalisation d'une mémoire à un électron par lithographie assistée par sonde en champ proche."

http://www.gpec.univ-mrs.fr/nanostructures/pages/set.html

"Dans le cadre du programme européen FASEM dont le but est la réalisation d'une mémoire à un électron, notre groupe de Nanotechnologie explore la possibilité d'utiliser les microscopies en champ proche (STM,AFM,SNOM) pour l'étape de lithographie à l'échelle nano-métrique." http://www.gpec.univ-mrs.fr/perso/marchi/marchi.htm

"Mémoire à un électron - Trouver des solutions nouvelles pour suivre la course à la miniaturisation tel est l'objectif des programmes de l'électronique du futur" http://www.grenoble-isere.com/cgi-bin/aepi/charge.pl

"L'électronique à un électron" http://www-drecam.cea.fr/ComScience/Phases/phases_09/p9article2.html