Transistor à un électron

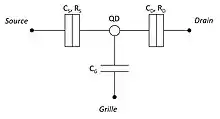

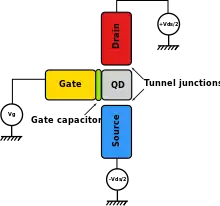

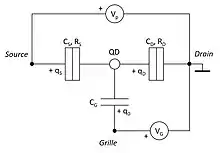

Le transistor à un électron (Single-electron transistor, SET) est un dispositif électronique basé sur l’effet de blocage de Coulomb. Dans un tel composant, les électrons traversent par effet tunnel une jonction source/drain, via une boîte quantique (îlot conducteur plus communément connu sous son appellation anglophone quantum dot, ou QD). Le potentiel électrique du quantum dot peut être contrôlé par une troisième électrode, ou grille, à laquelle il est lié par un couplage capacitif. La boîte quantique est placée entre deux jonctions tunnel [1], chacune étant modélisée par une capacitance (CD et CS) et une résistance (RD et RS) parallèles.

Histoire

Un nouveau champ d’étude de la physique de la matière condensée s’est ouvert en 1977, quand David Thouless a montré que la taille d’un conducteur, si elle est suffisamment petite, influe sur ses propriétés électroniques[2]. Le champ de recherche qui a suivi dans les années 1980, s’intéressant aux systèmes sub-microniques, est aussi appelé physique mésoscopique[3]. Il est le point de départ de travaux sur les transistors à un électron.

Le premier transistor à un électron basé sur le blocage de Coulomb est rapporté en 1986 par les chercheurs K. K. Likharev and D. V. Averin[4]. Quelques années plus tard, T. Fulton et G. Dolan des Bell Labs aux États-Unis démontrent le fonctionnement d’un tel composant[5]. En 1992, Marc A. Kastner souligne l’importance des niveaux d’énergie de la boîte quantique[6]. À la fin des années 1990 et au début des années 2000, les physiciens russes S. P. Gubin, V. V. Kolesov, E. S. Soldatov, A. S. Trifonov, V. V. Khanin, G. B. Khomutov, et S. A. Yakovenko sont les premiers à réaliser un SET basé sur des amas moléculaires et fonctionnant à température ambiante[7].

Intérêt

Le développement important de l’internet des objets (ou IoT : Internet of Things) et des applications médicales pose avec acuité la question de la consommation énergétique de ces composants. Leur large diffusion dans tous les aspects de la vie courante génère une consommation énergétique significative. L’électronique à très faible consommation d’énergie est ainsi devenue l’un des sujets de recherche majeurs dans le domaine des micro- et nano-technologies. Dans ce contexte, le transistor à un électron est un bon candidat pour combiner faible consommation d’énergie et densité de composants élevée.

Ils conviendraient entre autres pour les applications suivantes : électromètre à haute sensibilité, spectroscopie à un électron, étalon de courant continu, étalon de température, détection infrarouge, circuits logiques à contrôle en tension ou en courant, transistors programmable.

Composant

Principe

Les SET comportent, comme les FET, trois électrodes : la source, le drain et la grille. La différence principale entre les SET et les MOSFET, composants aujourd’hui les plus courants, se trouve dans l’architecture du canal entre source et drain. Le canal d’un FET peut passer d’un état isolant à un état conducteur lorsque la grille est polarisée ; à l’inverse, le canal du SET est toujours isolant. Le couplage source-drain se fait alors par deux jonctions tunnel, entre lesquelles se trouve un petit « îlot » de conduction, ou quantum dot (QD)[8]. La tension appliquée à la grille permet de contrôler le passage d’électrons vers le QD, grâce au phénomène de blocage de Coulomb.

Le courant source-drain répond à la loi d’Ohm quand une tension VSD est appliquée. Il est égal à VSD {R} , où la résistance vient principalement des transferts d’électrons par effet tunnel entre source et QD, et entre QD et drain. La tension de grille module la résistance du QD, qui va contrôler le courant. Ce comportement est identique à celui des FETs. Mais quand on s’éloigne de cette approche macroscopique, on peut décrire des effets quantiques dans ce courant .

Dans l'état de blocage, aucun niveau d'énergie accessible par les électrons de la source ne permet l'occurrence d'un effet tunnel (voir Fig.3 en rouge) entre un électron de l'électrode de source vers un état inoccupé de l'îlot. Puisque tous les niveaux d'énergie de l'îlot avec des énergies inférieures à celle de l'électrode de source sont déjà occupés, seuls des niveaux d'énergie supérieurs sont libres dans l'îlot.

Lorsqu'une tension positive est appliquée à l'électrode de porte, les niveaux d'énergie de l'électrode d'îlot sont abaissés. Ainsi maintenant, un électron de l'électrode de source (voir Fig.3 en vert, 1.) peut pénétrer dans l'îlot (2.), occupant un niveau d'énergie précédemment vacant car anciennement trop élevé. À partir de là, il peut pénétrer dans l'électrode de drain (3.) où il se diffuse de façon inélastique et atteint le niveau de Fermi de l'électrode de drain (4.). Les niveaux d'énergie de l'électrode de l'îlot sont espacés uniformément avec une séparation de . Ceci donne lieu à un auto-capacitance de l'îlot, défini comme .

Théorie

La recherche sur les SETs est basée principalement sur la « théorie orthodoxe » qui pose trois hypothèses :

- L’énergie à l’intérieur de l’îlot est un continuum, ce qui se vérifie si et seulement si le quantum d’énergie Ek << kBT.

- Le temps de traversée d’un électron à travers la barrière de potentiel est négligeable devant les autres grandeurs temporelles. Cette hypothèse est valable pour les barrières typiques des SET, où τt ~10-15s.

- Les effets tunnels concomitants sont négligés. Ceci est valable si la résistance de toutes les barrières de potentiel du système est largement supérieure à la résistance quantique nécessaire au confinement des électrons dans le quantum dot (~26 kΩ).

Plaçons-nous tout d’abord dans le cas d’un système de deux jonctions tunnel en série, polarisées par une tension . La grille (diélectrique entourant le QD) n’est donc pas polarisée, et on note la charge parasite de ce diélectrique. et sont les nombres d’électrons transférés dans les jonctions tunnel Source-QD et QD-Drain respectivement. Les charges accumulées par les barrières de potentiel associées sont données par :

où et sont les capacités correspondantes. Le nombre d’électrons en excès sur le QD est noté . On peut alors définir la charge du QD par :

La tension de polarisation étant on peut calculer les tensions aux bornes des deux jonctions tunnel :

D’où l’énergie électrostatique stockée par la double jonction tunnel (telle qu’illustrée sur le schéma) qui est :

Par ailleurs, la source de polarisation source-drain fourni un travail pour compenser les déséquilibres de charge lors du passage des électrons dans les jonctions tunnel. Celui-ci se définit pour chaque jonction comme :

Une approche thermodynamique du transfert des électrons à travers les jonctions tunnel se base sur l’équation d’énergie libre de Helmholtz :

- , où

Appliquée au SET, grâce aux équations d’énergie électrostatique et de travail obtenues, cette énergie libre devient :

On s’intéresse également, pour la suite, à la variation d’énergie libre induite par les transitions tunnel d’électron à température nulle :

La probabilité d’un transfert de charge apparaît lorsque la variation d’énergie est négative (relaxation du système). Elle le devient lorsque la tension de polarisation atteint une valeur seuil, qui sera conditionnée par la plus petite capacitance du système ( ou ). Généralement, pour un QD non chargé ( et ) et pour des barrières de potentiel symétriques ( ), on obtient la condition :

(on remarquera que la tension de seuil diminue de moitié par rapport à un transfert tunnel unique). Quand la tension de polarisation est nulle, le niveau de Fermi des électrodes sera inférieur à la bande passante du QD. Quand la tension de polarisation atteint le niveau seuil, des transferts d’électrons ont lieu de la source vers le drain.

La présence d’un blocage de Coulomb est clairement visible sur la caractéristique courant-tension d’un SET (graphe montrant la dépendance du courant de drain à la tension de polarisation). Pour de faibles tensions (en valeur absolue), le courant de drain sera nul. Pour des tensions au-delà de la tension seuil, les transferts tunnel apparaissent et le courant de drain devient linéaire avec la tension (comportement ohmique).

Souvenons-nous maintenant que, d’après la troisième hypothèse ci-dessus, la résistance des jonctions est supérieure au quantum de résistance : . Une discrétisation des transferts d’électron va alors se produire. Un électron qui franchira la première barrière vers le QD, se verra retenu sur l’îlot un certain temps avant de pouvoir franchir la deuxième barrière. Lorsqu’il aura libéré le QD, un électron pourra venir prendre sa place. Ainsi, la plupart du temps, le QD porte une charge en excès.

Ajoutons maintenant une polarisation à l’électrode de contrôle (la grille). Elle est liée au QD par une capacité et la tension de grille permet d’ajouter une charge de polarisation à la charge parasite du diélectrique. La charge du QD devient alors :

En introduisant cette équation modifiée dans les calculs ci-dessus, on trouve les nouvelles expressions des tensions aux bornes de chacune des jonctions :

L’énergie électrostatique doit maintenant inclure l’énergie de la capacitance de grille, et le travail fourni par la tension de grille doit être inclus dans les équations de libre énergie :

Là encore, à température nulle, seules les transitions avec une variation de libre énergie négative sont possibles : or . Ces conditions peuvent être utilisées pour trouver les zones de stabilité dans le plan .

Si l’on augmente la tension de grille, tout en gardant la tension de polarisation sous le seuil au-dessus duquel le blocage de Coulomb disparaît (i.e. ), alors le courant de drain en sortie oscillera selon une période .

Contraintes de fabrication

Les avantages principaux des SETs sont leur faible consommation d’énergie et leur densité d’intégration élevée. Mais leur principe de fonctionnement pose aussi des contraintes à leur mise en œuvre, comme les très faibles intensités de courant générées et la température de fonctionnement.

Dépendance à la température

Des transistors à un électron ont été réalisés avec plusieurs matériaux (en). Cependant, la température est un facteur limitant important pour leur intégration dans les composants électroniques. La plupart des SET à base de métaux ne fonctionnent qu’à des températures cryogéniques.

Pour éviter des fluctuations thermiques perturbant le blocage de Coulomb, l’énergie de charge électrostatique doit être supérieure à . En conséquence, la capacitance maximale autorisée de la boîte quantique est inversement proportionnelle à la température, et doit rester inférieure à 1 aF pour que le SET fonctionne à température ambiante.

La capacitance d’un quantum dot est fonction de sa taille, et son diamètre devrait être inférieur à 10 nm pour un fonctionnement dans ces conditions. Ceci engendre des contraintes de fabrication importantes, avec notamment des problèmes de reproductibilité pour de si petites dimensions.

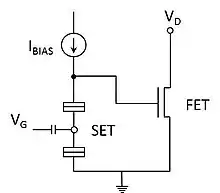

Compatibilité CMOS

Afin de pouvoir intégrer des SETs dans des composants de technologie CMOS, l’intensité de leur courant doit être amplifiée. Ceci peut être réalisé par des structures hybrides SET-FET (Fig.6). [9] - [10]

Développement d’un procédé de fabrication

Il n’y a pas à ce jour de procédé de fabrication industrialisable de tels circuits hybrides, fonctionnant à température ambiante. L’enjeu est de combiner la réalisation de structures SET aux dimensions extrêmement petites, avec des procédés de fabrication de grande échelle compatibles avec la fabrication de dispositifs CMOS. Ceci induit des contraintes notamment dans le choix :

- des équipements de fabrication : les outils adaptés aux très hautes résolutions n’ont pas forcément le flux de production suffisant

- des matériaux utilisés : les métaux utilisables sont restreints aux métaux compatibles avec les procédés CMOS.

L’intérêt pour les circuits à base de SETs a été récemment illustré par le financement, en 2016 et pour une durée de 4 ans, du projet IONS4SET (#688072) par l’Union Européenne.

L’enjeu de ce projet est de faciliter l’utilisation d’architectures hybrides SET-CMOS. Pour cela, il s’est fixé comme objectif de définir des procédés de fabrication industrialisables permettant d’obtenir des circuits SET-FET fonctionnant à température ambiante. Pour satisfaire ce critère de température, il est nécessaire d’obtenir des nanodots d’un diamètre inférieur à 5 nm, et placés entre la source et le drain avec des largeurs de barrières de potentiel de quelques nanomètres. . [11] La voie retenue par ce projet européen pour atteindre cet objectif est la fabrication de nano-plots multi-couche d’un diamètre d’environ 10 nm, combinée à la génération des nanodots par implantation ionique.

Références

- S. Mahapatra, V. Vaish, C. Wasshuber, K. Banerjee, and A. M. Ionescu, “Analytical Modeling of Single Electron Transistor for Hybrid CMOS-SET Analog IC Design,” IEEE Trans. Electron Devices, vol. 51, no. 11, p. 1772–1782, novembre 2004.

- Thouless, David J. (1977). "Maximum Metallic Resistance in Thin Wires". Phys. Rev. Lett. 39 (18): 1167–1169. Bibcode:1977 PhRvL..39.1167T.

- Al'Tshuler, Boris L.; Lee, Patrick A. (1988). "Disordered electronic systems". Physics Today. 41 (12): 36–44. Bibcode:1988PhT....41l..36A.

- Averin, D. V.; Likharev, K. K. (1986-02-01). "Coulomb blockade of single-electron tunnelling, and coherent oscillations in small tunnel junctions". Journal of Low Temperature Physics. 62 (3–4): 345–373. Bibcode:1986JLTP...62..345A.

- "Single-electron transistors". Physics World. 1998-09-01. Retrieved 2019-09-17.

- Kastner, M. A. (1992-07-01). "The single-electron transistor". Rev. Mod. Phys. 64 (3): 849–858. Bibcode:1992RvMP...64..849K. doi:10.1103/RevModPhys.64.849.

- Gubin, S. P.; Gulayev, Yu V.; Khomutov, G. B.; Kislov, V. V.; Kolesov, V. V.; Soldatov, E. S.; Sulaimankulov, K. S.; Trifonov, A. S. (2002). "Molecular clusters as building blocks for nanoelectronics: the first demonstration of a cluster single-electron tunnelling transistor at room temperature". Nanotechnology. 13 (2): 185–194. Bibcode:2002Nanot..13..185G. doi:10.1088/0957-4484/13/2/311.

- K. Uchida, K. Matsuzawa, J. Koga, R. Ohba, S. I. Takagi, and A. Toriumi, “Analytical single-electron transistor (SET) model for design and analysis of realistic SET circuits,” Jpn. J. Appl. Phys., vol. 39, no. 4 B, p. 2321–2324, 2000.

- Ionescu, A.M.; Mahapatra, S.; Pott, V. (2004). "Hybrid SETMOS Architecture With Coulomb Blockade Oscillations and High Current Drive". IEEE Electron Device Letters. 25 (6): 411–413. Bibcode:2004IEDL...25..411I. doi:10.1109/LED.2004.828558. ISSN 0741-3106.

- Amat, Esteve; Bausells, Joan; Perez-Murano, Francesc (2017). "Exploring the Influence of Variability on Single-Electron Transistors Into SET-Based Circuits". IEEE Transactions on Electron Devices. 64 (12): 5172–5180. Bibcode:2017ITED...64.5172A. doi:10.1109/TED.2017.2765003. ISSN 0018-9383.

- Klupfel, F. J.; Burenkov, A.; Lorenz, J. (2016). "Simulation of silicon-dot-based single-electron memory devices". 2016 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD). p. 237–240.