POWER8

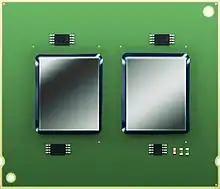

Le POWER8 est un processeur de la gamme POWER conçu et produit par IBM et annoncé en . Il est gravé en technologie 22 nm, avec une fréquence d'horloge maximum de 4,15 GHz.

Une des principales nouveautés annoncées par IBM est la possibilité offerte à des tiers fabricants de composants d'ajouter des éléments dans la nouvelle génération de serveurs à base de POWER8[1], en particulier en partenariat avec Google[2].

Caractéristiques techniques

Le POWER8 peut supporter jusqu'à 1 To de DRAM et offre 230 Go/s de bande passante mémoire (soit le double des POWER7), et 96 Go/s d'entrées-sorties. Chaque puce comporte 12 cœurs, un cœur supporte 8 threads, ce qui permet d'aller jusqu'à 96 threads par puce[3]. Le niveau de multithreading peut être modifié par les différents systèmes d'exploitation s'exécutant sur les POWER8 (AIX, IBM i et Linux).

4 niveaux de multithreading sont donc possibles : SMT1, SMT2, SMT4 et SMT8. Cela permet d'activer 1, 2, 4 ou 8 threads par cœur.

Il existe 4 niveaux de cache sur le processeur POWER8 :

- Le niveau de cache L1, par cœur, est de 32 Ko pour les instructions et de 64 Ko pour les données.

- Le niveau de cache L2 est de 512 Ko par cœur.

- Le niveau de cache L3 est de 8 Mo par cœur soit 96 Mo pour le processeur.

L'une des multiples nouveautés du POWER8 est l'implémentation d'un niveau de cache supplémentaire de niveau L4.

- Le niveau de cache L4 est de 128 Mo. Ce cache n'est pas directement sur la puce, contrairement aux caches de niveau L1, L2 et L3, il est dit off-chip à l'opposé de on-chip pour les autres caches.

La surface de ce processeur est de 649 mm2, soit un peu plus grand que son prédécesseur le POWER7/POWER7+ qui faisait 567 mm2.

Il supporte la technologie SR-IOV (Single Root I/O Virtualization) permettant la virtualisation des cartes PCIe.

Le POWER8 dispose d’un processeur PowerPC embarqué avec son propre cache de 512 Ko qui est utilisé comme un contrôleur embarqué en temps réel pour son micrologiciel. Ce micrologiciel analyse les modifications des charges qui s’exécutent sur le POWER8 et ajuste la fréquence et la tension des cœurs pour optimiser les performances ou la consommation électrique. Son temps de réaction est 100 fois plus rapide que les modifications des charges, ce qui généralement bien plus rapide que les ordonnanceurs des systèmes d'exploitation.

Chaque POWER8 dispose de 8 canaux mémoire high-speed à 9,6 GHz et chaque puce Centaur peut gérer 4 ports DDR3 soit 410 Gbit/s de bande passante.

Il dispose de 16 pipelines :

- 2 FXU (Fixed-Point Units)

- 2 LSU (Load Store Units)

- 2 LU

- 4 FPU

- 2 VMX (Vector Math Units)

- 1 Crypto

- 1 DFU (Decimal Floating Unit)

- 1 CRU (Condition Register Unit)

- 1 BRU (Branch Register Unit)

L’interconnexion SMP entre les books d'un système multi-processeur a été totalement revue. Chaque processeur a un lien direct avec les processeurs du même book et un lien direct avec chaque processeur de même niveau des autres books.

Il supporte jusqu'à 20 machines virtuelles par cœur, c'est-à-dire 5 % minimum par tranche de temps processeur (10 ms).

Son successeur, le POWER9, est prévu pour la fin de la décennie (2019/2020) et devrait être gravé à 14 nm.

Usages

Le processeur est proposé par certains hébergeurs au sein de leur serveur pour héberger des machines virtuelles (Linux POWER, AIX ou IBM i ?). C'est le cas de l'hébergeur OVH via son offre RunAbove[4], qui propose jusqu'à 176 threads.

Voir aussi

Notes et références

- « Avec le Power8, IBM entame une véritable révolution culturelle - Le Monde Informatique », sur Le Monde informatique (consulté le ).

- (en) computerworld

- « IBM détaille un peu la prochaine puce Power8 - Le Monde Informatique », sur Le Monde informatique (consulté le ).

- http://labs.runabove.com/power8/

Liens externes

- (en) Présentation technique POWER8 [PDF]