POWER4

Le POWER4 est un microprocesseur qui implémente l'architecture 64-bit PowerPC. Sorti en 2001, il est fondé sur la conception de son prédécesseur, le POWER3. Le POWER4 est un microprocesseur multi-cœur, avec deux cœurs sur la même puce, le premier de ce genre.

Architecture interne

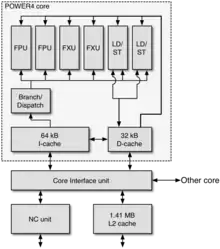

L'unité interne du POWER4 consiste en deux implémentations de l'architecture PowerPC AS. Le POWER4 a deux caches de niveau 2 unifiés, divisés en trois parties égales. Chacun d'eux à son propre contrôleur de cache de niveau 2 indépendant qui peut chercher 32 octets de données par cycle. La Core Interface Unit (CIU, unité d'interface principale), connecte chaque contrôleur de cache au cache de données ou au cache d'instructions des deux processeurs. L'unité Non-Cacheable (NC), s'occupe de la gestion de la sérialisation des instructions et de toutes les opérations qui ne sont pas cachables dans la topologie des enregistrements. Il y a un contrôleur de cache de niveau 3, mais il est situé en fait en dehors de la puce. Le contrôleur de bus GX pilote les entrées/sorties, les communications, et les deux bus GX 32bits, un en entrée et l'autre en sortie. Le Fabric Controller est le contrôleur principal du réseau de bus, des communications entre les contrôleurs de caches, des communications entre les puces POWER4, et des modules de POWER. Le processeur contient aussi le nécessaire au débogage (Built In Self Test function, BIST) et à la mesure de performances avec la Performance Monitoring Unit (PMU). Le Power-on reset est aussi supporté.

Unités d'exécution

Le POWER4 implémente une architecture superscalaire en utilisant huit unités d'exécution spéculatives out of order (dans le désordre) à haute fréquence : deux unités virgule flottante (FP1-2), deux unités load-store (LD1-2), deux unités de calculs entiers (FX1-2), une unité de gestion des branchements (BR-1) et une unité de gestion des registres conditionnels (CR). Ces unités peuvent compléter jusqu'à huit opérations par cycle (sans les unités BR et CR) :

- chaque unité virgule flottante peut compléter une multiplication/addition par cycle (deux opérations) ;

- chaque unité load-store peut compléter une instruction par cycle ;

- chaque unité de calcul entier peut compléter une instruction par cycle.

Les étapes du pipeline sont :

- prédictions des branches ;

- recherche d'une instruction (fetch) ;

- décodage, éclatement des instructions et formation de groupes ;

- réorganisation des groupes ;

- opérations de chargement/stockage (load/store) ;

- exécution de l'instruction du pipeline.

Configuration multipuce

Le POWER4 vient aussi sur des modules multipuces qui contiennent quatre POWER4 sur le même circuit intégré.

Notes et références

Voir aussi

Articles connexes

Bibliographie

- (en) J. M. Tendler, J. S. Dodson, J. S. Fields, Jr., H. Le, and B. Sinharoy, « POWER4 system microarchitecture », IBM Journal of Research and Development, vol. 46, no 1, , p. 5–26 (ISSN 0018-8646, DOI 10.1147/rd.461.0005, lire en ligne, consulté le )

- (en) J. D. Warnock, J. M. Keaty, J. Petrovick, J. G. Clabes, C. J. Kircher, B. L. Krauter, P. J. Restle, B. A. Zoric, and C. J. Anderson, « The circuit and physical design of the POWER4 microprocessor », IBM Journal of Research and Development, vol. 46, no 1, , p. 27–52 (ISSN 0018-8646, DOI 10.1147/rd.461.0027, lire en ligne, consulté le )