Circuit intégré 74184

Le circuit intégré 74184 fait partie de la série des circuits intégrés 7400 utilisant la technologie TTL. Ce circuit est un convertisseur BCD (décimal codé binaire) vers binaire. La fonction logique qu'il réalise est purement combinatoire.

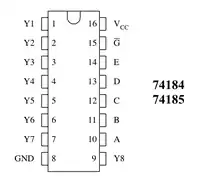

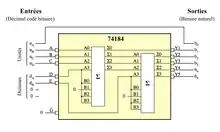

Le 74184 présente 5 entrées de données (A à E), 8 sorties de données à collecteur ouvert (Y1 à Y8) et une entrée d'invalidation des sorties (G).

Lorsque l'entrée G est portée à l'état haut, toutes les sorties du circuit sont forcées à l'état logique haut. S'agissant de sorties à collecteur ouvert, du point de vue électrique elles sont passées dans un état à haute impédance.

Le 74184 permet de réaliser l'une des trois opérations suivantes :

- la conversion d'un nombre décimal codé binaire (BCD) compris entre 0 et 39 vers un nombre binaire naturel de 6 bits ;

- la conversion d'un nombre décimal codé binaire (BCD) compris entre 0 et 9 vers son complément à 9 au format décimal codé binaire (BCD) ;

- la conversion d'un nombre décimal codé binaire (BCD) compris entre 0 et 9 vers son complément à 10 au format décimal codé binaire (BCD).

En interne, le circuit produit le résultat de ces opérations à l'aide d'une mémoire ROM de 256 bits (32 octets) à adressage et sorties parallèles de type 7488 qui contient les données binaires nécessaires.

Conversion vers binaire naturel

Mise en œuvre pour la conversion d'un nombre décimal de 0 à 39.

Le bit de poids faible reste inchangé dans cette conversion. Il n'est pas traité par le circuit, qui ne reçoit donc du nombre à convertir que les 3 bits de poids fort du chiffre des unités sur ses entrées A, B et C (poids 21 à 23 resp.), et les deux bits de poids du chiffre des dizaines sur ses entrées D et E (poids 10×20 et 10×21 resp.).

Les sorties Y1 à Y5 produisent les 5 bits de poids fort du résultat binaire (poids 21 à 25 resp.), le bit de poids faible étant obtenu par simple recopie du bit de poids faible du nombre décimal (poids 20).

Les sorties Y6 à Y8 ne sont pas utilisées dans cette conversion.

D'un point de vue logique, dans ce mode, le fonctionnement du circuit est équivalent à l'enchaînement de deux étapes élémentaires de l'algorithme de conversion dont chaque itération consiste à décaler l'ensemble du nombre d'un bit vers les poids faibles puis à ôter 3 à chaque décade dont la valeur est supérieure à 7.

La combinaison de plusieurs circuits 74184 permet de réaliser la conversion de nombres décimaux supérieurs à 39. Par exemple, un nombre décimal à deux chiffres (0 à 99) peut être converti en binaire (7 bits) à l'aide de deux boîtiers 74184, et un nombre décimal à trois chiffres (0 à 999) peut être converti en binaire (10 bits) à l'aide de six boîtiers.

Conversion vers complément à 9

Pour cette opération, le circuit doit recevoir un niveau bas (0 logique) sur son entrée E et les 4 bits du nombre décimal à convertir sur ses entrés A, B, C et D (poids 20 à 23 resp.).

Le deuxième bit de poids faible (poids 21) restant inchangé dans cette conversion, il produit directement le deuxième bit de poids faible du résultat (poids 21).

La sortie Y6 produit le bit de poids faible du résultat (poids 20) et les sorties Y7 et Y8 ses bits de poids fort (poids 22 et 23 resp.).

Les sorties Y1 à Y5 ne sont pas utilisées dans cette conversion.

Conversion vers complément à 10

Pour cette opération, le circuit doit recevoir un niveau haut (1 logique) sur son entrée E et les 4 bits du nombre décimal à convertir sur ses entrés A, B, C et D (poids 20 à 23 resp.).

Le bit de poids faible (poids 20) restant inchangé dans cette conversion, il produit directement le bit de poids faible du résultat (poids 20).

La sortie Y6 à Y8 produisent le bit de poids fort du résultat (poids 21 à 23 resp.).

Les sorties Y1 à Y5 ne sont pas utilisées dans cette conversion.

Lorsque les niveaux logiques appliqués sur les entrées ne correspondent pas à un nombre décimal valide, les sorties du circuit produisent un niveau haut (s'agissant de sorties à collecteur ouvert, elles passent dans un état à haute impédance).

Contrairement à la plupart des circuits TTL de la série 7400, le 74184 n'a pas été décliné en version CMOS (familles 74C00, 74HCT00, 74HC00 et dérivées).

Voir aussi

Liens externes

- Spécifications des circuits SN54/74184 et SN54/74185A (The TTL Data Book Vol. 2, Texas Instruments, 1985 - pages 3-731 et suivantes)

- Spécifications des circuits DM74184 et DM74185A (LS/S/TTL Databook, National Semiconductor, 1989 - pages 4-201 et suivantes)