Chip select

On nomme chip select une entrée de contrôle de nombreux circuits intégrés, tels que les puces mémoires, permettant d'activer ou désactiver le circuit. Quand elle est active, le composant peut être adressé ; quand elle ne l'est pas, le composant est dans un mode dit standby (au repos). L'économie d'énergie qui en découle est appréciable, surtout quand le nombre de circuits désactivés est important (ce qui est le cas pour les puces formant la mémoire centrale d'un ordinateur par exemple).

Exemple pratique immédiat

Lorsque vous assemblez un système à microprocesseur et que vous devez monter une ROM ou une RAM (puces) à l'adresse hexadécimale 4000, vous êtes typiquement confronté à un problème de chip select.

Autre exemple

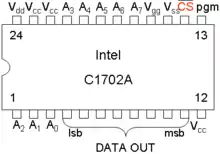

Voici le brochage de l'EPROM Intel C1702A. La patte numéro 14 est le Chip Select, noté CS. La consommation est de 35 mA versus 5 mA quand la puce est inactivée par la biais du Chip Select.

La puce Intel C1702A. |

Le brochage de la puce Intel C1702A. La patte 14 est le Chip Select, actif quand il est à 0 V. |

Mise en application

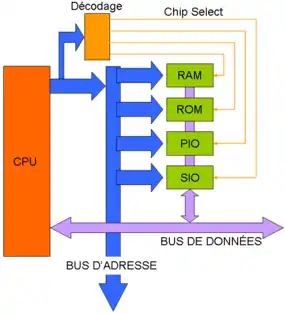

Suivant le nombre de fils que possède le bus d'adresse d'un microprocesseur, on peut déterminer la taille mémoire maximum qu'il peut adresser. Par exemple s'il possède 16 fils d'adresse, il pourra accéder à 64 Kmots (216 mots) de mémoire.

Le bus d'adresse est donc décodé pour contrôler la ligne chip select des puces qui y sont reliées. Il y a plusieurs façons de décoder les adresses :

Décodage direct

Il suffit de prendre directement les fils d'adresses pour activer les composants. Cela n'est possible que dans les cas où l'adressage est très simple comme par exemple un microprocesseur qui adresse 4 Ko de ROM et 1 Ko de RAM, sans aucune autre contrainte.

Si l'on raccorde directement le fil A14 du bus d'adresse à la broche Chip Select de la ROM et le fil A12 du bus d'adresse à la broche chip select de la RAM, ces deux espaces mémoire seront accessibles comme suit :

| Mémoire | Fil d'adresse | Plage d'adresses |

|---|---|---|

| ROM | A14 | 16 K - 20 K |

| RAM | A12 | 4 K - 5 K |

Un autre argument en la faveur de cette technique est l'économie réalisée, le nombre de circuits extérieurs étant nul.

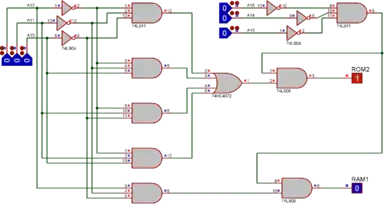

Décodage par logique combinatoire

Reprenons le cas du montage précédent, mais on a maintenant la contrainte que les 4 Ko de ROM doivent être accessibles à partir de l'adresse 0, et les 1 K de RAM contigüe, toute la mémoire étant ainsi accessible entre 0 et 5 Ko.

Découpons la mémoire en tranches de 1 K, et assignons les 4 premières à la ROM et la dernière à la RAM. Les adresses sont alors :

| A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | ROM | ||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 | 0 | x | x | x | x | x | x | x | x | x | x | 2 K - 3 K | 0x800 - 0xBFF | ROM |

| 0 | 0 | 0 | 0 | 1 | 1 | x | x | x | x | x | x | x | x | x | x | 3 K - 4 K | 0xC00 - 0xFFF | ROM |

| 0 | 0 | 0 | 1 | 0 | 0 | x | x | x | x | x | x | x | x | x | x | 4 K - 5 K | 0x1000 - 0x13FF | RAM |

| x | x | x | 1 | x | x | x | x | x | x | x | x | x | x | x | x | 5 K - 64 K | 0x1400 - 0xFFFF | \x{2014} |

Il faut donc construire un circuit à 6 entrées (de A10 à A15) et 2 sorties CSROM et CSRAM qui contrôleront chacune la broche Chip Select de la ROM et de la RAM.

On constate qu'il faut une dizaine de circuits intégrés pour décoder l'adresse.

Cette technique revient à décomposer l'adresse en deux parties : les N bits de poids fort permettront la sélection du circuit via son Chip Select, et les bits de poids faible à adresser les données à l'intérieur du circuit sélectionné. Cette méthode est à rapprocher de la technique de la pagination de la mémoire virtuelle.

| Bits de Sélection | Adressage à l'intérieur de l'objet sélectionné | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

| 0 | 0 | 0 | 0 | 0 | 0 | x | x | x | x | x | x | x | x | x | x |

| 0 | 0 | 0 | 0 | 0 | 1 | x | x | x | x | x | x | x | x | x | x |

| 0 | 0 | 0 | 0 | 1 | 0 | x | x | x | x | x | x | x | x | x | x |

| 0 | 0 | 0 | 0 | 1 | 1 | x | x | x | x | x | x | x | x | x | x |

| 0 | 0 | 0 | 1 | 0 | 0 | x | x | x | x | x | x | x | x | x | x |

| 0 | 0 | 0 | 1 | 0 | 1 | x | x | x | x | x | x | x | x | x | x |

| 0 | 0 | 0 | 1 | 1 | 0 | x | x | x | x | x | x | x | x | x | x |

| \x{2014} | \x{2014} | \x{2014} | \x{2014} | \x{2014} | \x{2014} | x | x | x | x | x | x | x | x | x | x |

| 1 | 1 | 1 | 1 | 1 | 1 | x | x | x | x | x | x | x | x | x | x |

Décodage partiel

Dans l'exemple précédent, on remarque que le bit A12 est discrimant. On peut donc tout simplement l'utiliser pour partiellement décoder l'adresse : on économisera des circuits. Mais, par exemple, l'adresse 0xFxxx sélectionnera la RAM, alors que ce n'est pas son adresse. On a donc créé des zones images de la RAM et de la ROM.

Utilisation d'un décodeur

Des circuits intégrés spéciaux ont été conçus pour prendre en charge le décodage d'adresse, on les appelle donc simplement décodeurs ou bien parfois démultiplexeurs. Ils possèdent N entrées et 2N sorties.

Voici la table de vérité pour un décodeur «3 vers 8» :

| A | B | C | S0 | S1 | S2 | S3 | S4 | S5 | S6 | S7 | ||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | ||

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | ||

| 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | ||

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | ||

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | ||

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | ||

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | ||

Celui-ci vient donc tout naturellement s'interfacer sur le bus d'adresse, d'où les N fils de poids fort iront vers l'entrée du décodeur, tandis que les 2N fils de sorties contrôleront les broches Chip Select des circuits.

L'usage d'un décodeur implique que les blocs mémoires accédés soient de même taille.

Autres méthodes

- On peut utiliser une mémoire morte pour faire la sélection. Dans notre exemple ci-dessus, pour complètement décoder l'adresse, il suffit d'une mémoire de 64 x 2 bits dont le premier fil de sortie sera relié sur le Chip Select de la ROM et le second sur celui de la RAM. La mémoire contiendra la valeur 10 pour les adresses entre 0 et 4 K et 01 aux adresses entre 4 et 5 K et 00 au-delà. L'inconvénient de l'utilisation de table de translation implanté sous forme de mémoire morte est qu'elle peut être d'assez grande capacité si beaucoup de bits sont utilisés pour décoder.

- Une PAL plus ou moins complexe est aussi parfois utilisée.