Protocole de cohérence de cache

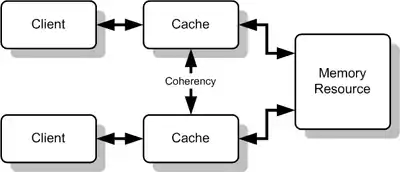

En informatique, un protocole de cohérence de cache, sous entendu cache processeur, est un protocole de communication utilisé dans les architectures multi-processeurs pour assurer aux processeurs une vue cohérente de la mémoire. En particulier, il permet de répercuter les écritures faites par chaque processeur aux autres, en modifiant ou en invalidant les lignes de cache communes.

Il existe deux grandes familles de protocoles de cohérence de cache : par espionnage, basés sur la surveillance des modifications faites par tous les autres processeurs, ou par répertoire, qui stockent des informations sur chaque portion de la mémoire (les caches où elle est dupliquée, si elle a été modifiée, etc.).

Cohérence par espionnage

Un protocole de cohérence par espionnage (snooping-based) utilise un bus commun, ce qui permet à chaque processeur de surveiller les accès à la mémoire des autres. Il invalide la ligne correspondante dans son cache lors d'une écriture par un autre processeur.

Cohérence par répertoire

Un protocole de cohérence par répertoire (directory-based) stocke les informations d'emplacement et d'état pour chaque portion de mémoire de la taille d'une ligne de cache. Il existe plusieurs moyens pour répartir ces données, soit en utilisant une unique mémoire, soit en distribuant celle-ci, soit enfin en utilisant une organisation hiérarchique, chaque nœud possédant les informations sur les lignes de cache présentes chez ses fils.

Notes et références

Voir aussi

Des protocoles de cohérence de cache :