Circuit intégré 7400

Le circuit intégré 7400[1] fait partie de la série des circuits intégrés 7400 utilisant la technique TTL.

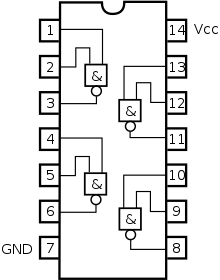

Ce circuit est composé de quatre portes logiques indépendantes NON-ET à deux entrées.

Brochage

(vue du dessus)

Table de vérité

| Entrées | Sortie | |

|---|---|---|

| A | B | Y |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

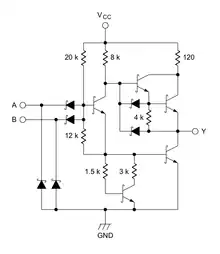

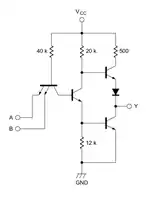

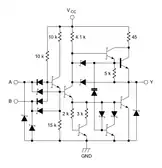

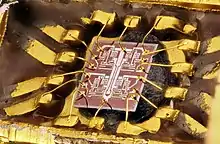

Schéma interne

La réalisation du circuit TTL 7400 varie en fonction de la série à laquelle il appartient (standard, L, S, LS, AS...). Chaque série présente des performances spécifiques (temps de propagation, consommation électrique, immunité au bruit, protections...) destinées à répondre à des besoins déterminés (rapidité de fonctionnement, autonomie, résistance à des perturbations et à des environnements agressifs...) tout en restant compatible avec les circuits TTL des autres séries. Pour une série donnée, la réalisation du circuit varie également d'un constructeur à l'autre et au gré des améliorations technologiques.

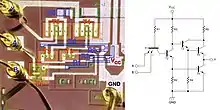

Ce schéma est repris dans les circuits de test des sorties totem-pole.

Les différentes variantes du circuit partagent la même architecture globale, à savoir :

- la mise en œuvre de transistors bipolaires saturés

- un opérateur logique ET à deux entrées (A et B) réalisé à l'aide de deux jonctions P-N reliées par leur anode à une résistance de rappel à VCC ; le niveau de tension au point commun à ces anodes et à la résistance de rappel (point [c]† dans l'illustration ci-contre) est représentatif du résultat logique de l'opération ET

- un amplificateur inverseur de type push-pull ("totem-pole") qui inverse le résultat logique précédent (opérateur NON) et produit sur la sortie (Y) une tension conforme au niveau TTL correspondant.

† Remarque : on trouve deux ou trois jonctions P-N en série (dont deux appartenant à l'amplificateur) entre le point [c] et la masse (GND) et une seule jonction P-N entre le point [c] et chaque entrée. Ces jonctions P-N présentant des tensions de seuil relativement faibles, cette configuration limite fortement la tension de basculement de la porte logique et, par conséquent, les tensions qui définissent les états logiques (état bas au-dessous de 0,8 V, état haut au-dessus de 2 V). Par ailleurs, l'application d'un niveau logique haut sur une entrée entraînant le blocage de la jonction P-N qui y est reliée, le courant d'entrée (statique) à l'état haut est quasiment nul (< 50 µA).

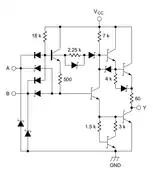

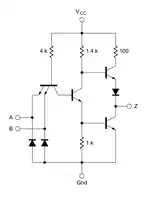

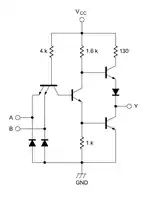

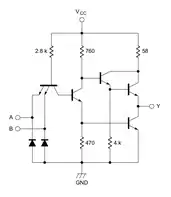

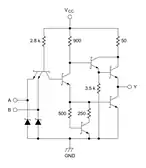

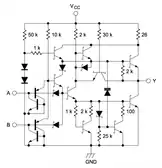

Différences de réalisation d'une porte 74LS00 (Low-power Schottky) entre les constructeurs et entre les références d'un même constructeur :

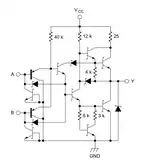

Schémas pour différentes séries :

Caractéristiques

Les caractéristiques électriques dépendent de la série TTL considérée, mais elles restent basées sur une définition commune des niveaux logiques afin de garantir la compatibilité entre les circuits des différentes séries TTL.

Les valeurs suivantes sont données à titre indicatif, car elles sont susceptibles de varier légèrement d'un constructeur à l'autre. Néanmoins, elles sont représentatives des valeurs constatées chez les différents constructeurs pour les circuits TTL de référence générique 74x00 (ou 54x00 pour les séries militaires) appartenant à une même série.

Tensions et courants

| Paramètre | Circuit | Unité | Conditions | |||||

|---|---|---|---|---|---|---|---|---|

| SN7400 | SN5400 | SN74LS00 | SN54LS00 | SN74S00 | SN54S00 | |||

| VCC(min) | 4,75 | 4,5 | 4,75 | 4,5 | 4,75 | 4,5 | V | |

| VCC(max) | 5,25 | 5,5 | 5,25 | 5,5 | 5,25 | 5,5 | V | |

| VIH | 2 | 2 | 2 | 2 | 2 | 2 | V | |

| VIL | 0,8 | 0,8 | 0,8 | 0,7 | 0,8 | 0,8 | V | |

| IOH | -0,4 | -0,4 | -0,4 | -0,4 | -1 | -1 | mA | |

| IOL | 16 | 16 | 8 | 4 | 20 | 20 | mA | |

| VOH | 2,4 | 2,4 | 2,5 | 2,5 | 2,5 | 2,5 | V | VCC=VCC(min) VI=VIL IO=IOH |

| VOL | 0,4 | 0,4 | 0,5 | 0,4 | 0,5 | 0,5 | V | VCC=VCC(min) VI=VIH IO=IOL |

| IIH | 40 | 40 | µA | VCC=VCC(max) VI=VOH | ||||

| 20 | 20 | 50 | 50 | µA | VCC=VCC(max) VI=2,7 V | |||

| IIL | -1,6 | -1,6 | -0,4 | -2 | -2 | mA | VCC=VCC(max) VI=VOL | |

| -0,4 | mA | VCC=VCC(max) VI=0,4 V | ||||||

(D'après Texas Instruments[1].)

| Notes : |

|---|

|

VCC : tension d'alimentation |

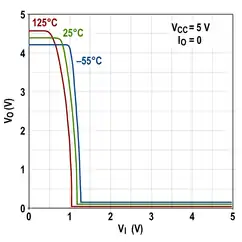

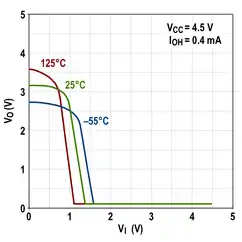

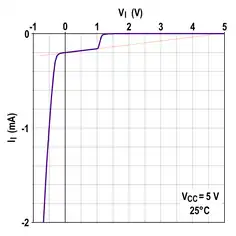

Caractéristique de transfert entrée-sortie

à différentes températures,

pour VCC=5 V et IOH=0

(d'après Fairchild Semiconductor[6]).

à différentes températures,

pour VCC=4,5 V et IOH=0,4 mA

(d'après Fairchild Semiconductor[7]).

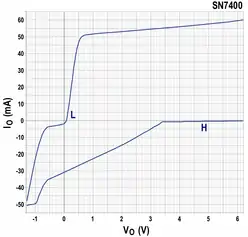

Caractéristiques tension-courant

H = sortie au niveau haut (1 logique)

L = sortie au niveau bas (0 logique)

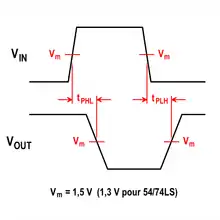

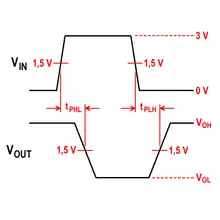

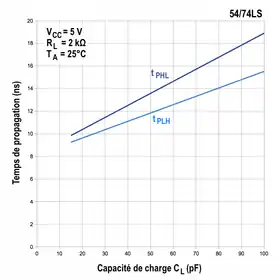

Temps de propagation

- D'après Fairchild Semiconductor[6] :

| Porte TTL | 54/7400 | 54/74H00 | 54/74S00 | 54/74LS00 | Unité | ||||

|---|---|---|---|---|---|---|---|---|---|

| Valeurs | min. | max. | min. | max. | min. | max. | min. | max. | |

| tPHL | – | 15 | – | 10 | 2.0 | 4.5 | – | 10 | ns |

| tPLH | – | 22 | – | 10 | 2.0 | 4.5 | – | 10 | ns |

| Conditions | CL=15 pF RL=400 Ω |

CL=15 pF RL=280 Ω |

CL=15 pF RL=280 Ω |

CL=15 pF – |

|||||

| Porte TTL | SN54/7400 | SN54/74H00 | SN54L00 | SN54/74S00 | SN54/74LS00 | Unité | |||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Valeurs | typ. | max. | typ. | max. | typ. | max. | typ. | max. | typ. | max. | |

| tPHL | 7 | 15 | 6,2 | 11 | 35 | 60 | 3 | 5 | 10 | 15 | ns |

| tPLH | 11 | 22 | 6,8 | 11 | 50 | 90 | 3 | 4.5 | 9 | 15 | ns |

| Conditions | CL=15 pF RL=400 Ω |

CL=25 pF RL=280 Ω |

CL=50 pF RL=4 kΩ |

CL=15 pF RL=280 Ω |

CL=15 pF RL=2 kΩ |

||||||

| Notes : |

|---|

|

Valeurs mesurées à TA = 25 °C (température ambiante) et VCC = 5 V |

Consommation de courant

| Circuit | ICCH | ICCL | Unité | ||

|---|---|---|---|---|---|

| typ. | max. | typ. | max. | ||

| SN54/7400 | 4 | 8 | 12 | 22 | mA |

| SN54/74LS00 | 0,8 | 1,6 | 2,4 | 4,4 | mA |

| SN54/74S00 | 10 | 16 | 20 | 36 | mA |

(D'après Texas Instruments[1].)

| Notes : |

|---|

|

ICCH : courant d'alimentation, sorties à l'état haut |

Références

- (en) SNx400, SNx4LS00, and SNx4S00 Quadruple 2-Input Positive-NAND Gates, Texas Instruments, 1983 rev. 2017

- (en) The TTL Data Book vol. 2, Texas Instruments 1985

- (en) LS/S/TTL Logic Databook, National Semiconductor 1989

- (en) TTL Integrated Circuits Data Book, Motorola 1971

- (en) FAST (Fairchild Advanced Schottky TTL) Data Book, Fairchild 1985

- (en) TTL Data Book Fairchild 1978

- (en) DC Electrical Characteristics of MM74HC high-Speed CMOS Logic, Fairchild 1998 (page 2, comparaison avec LS00)

- (en) Input and Output Characteristics of Digital Integrated Circuits, Texas Instruments, 1996