Circuit intégré 4011

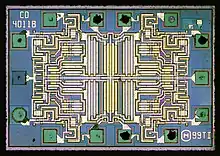

Le circuit intégré 4011[1] fait partie de la série des circuits intégrés 4000 utilisant la technologie CMOS.

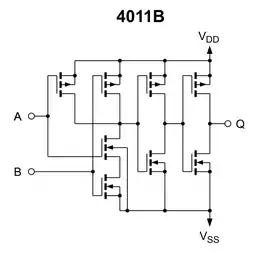

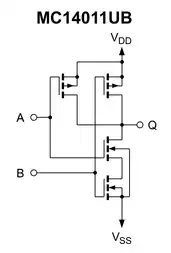

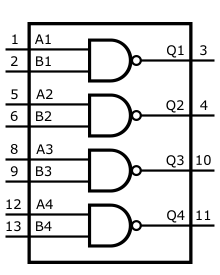

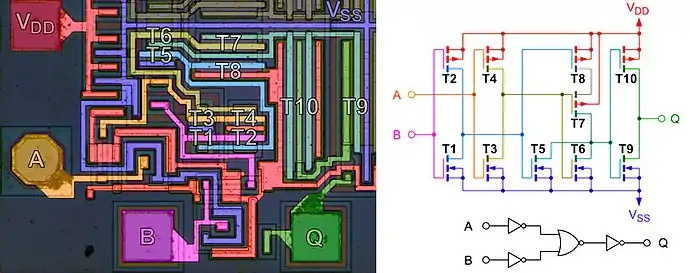

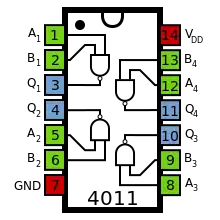

Ce circuit est composé de quatre portes logiques indépendantes NON-ET à 2 entrées.

Description

Diagramme

Entrées

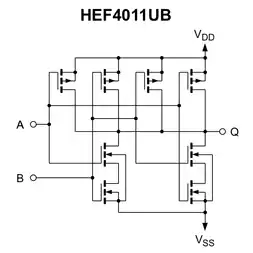

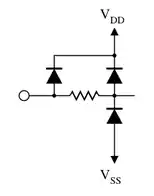

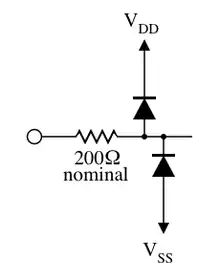

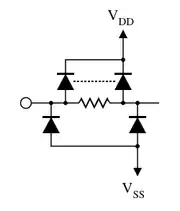

Chaque porte logique NAND possède 2 entrées (A et B). Chaque entrée présente un circuit de protection contre les surtensions et les décharges électrostatiques (ESD) constitué de diodes et d'une résistance.

Sorties

Chaque porte logique NAND possède une sortie (Q).

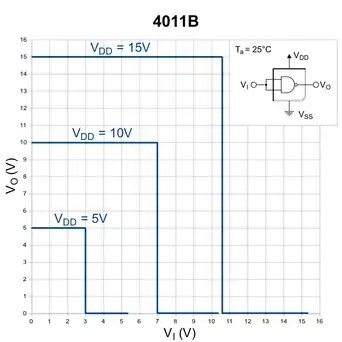

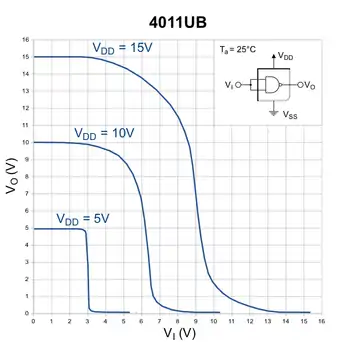

Dans les versions classiques du 4011, les sorties sont bufferisées, c'est-à-dire pourvues d'un tampon de sortie (amplificateur) améliorant la fonction de transfert du circuit. Dans les versions non bufferisées (4011UB), les sorties sont dépourvues de tampon, ce qui réduit d'environ de moitié le délai de propagation des portes logiques.

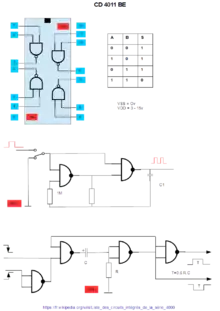

Table de vérité

| Entrées | Sortie | |

|---|---|---|

| A | B | Q |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Brochage

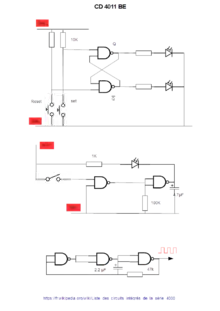

Applications

Galerie

Philips Semiconductor HEF4011BP (DIP14)

Philips Semiconductor HEF4011BP (DIP14)

Voir aussi

Références

- (en) « HCC4011B - Rad-hard quad 2-input NAND gate - STMicroelectronics », sur www.st.com (consulté le )