Circuit intégré 4006

Le circuit intégré 4006[1] - [2] - [3] - [4] fait partie de la série des circuits intégrés 4000 utilisant la technologie CMOS.

.svg.png.webp)

C'est un registre à décalage disposant de 4 registres :

- 2 registres de 4 bits

- 2 registres de 5 bits

Ces 4 registres peuvent être chaînés pour former un unique registre de 18 bits.

Description

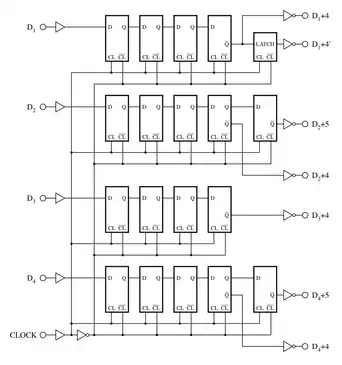

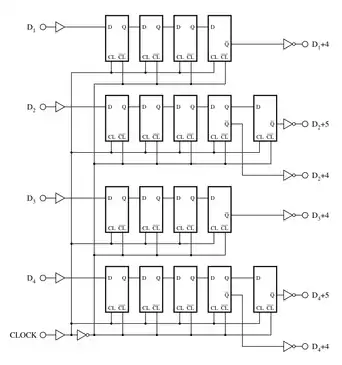

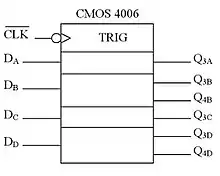

Diagramme

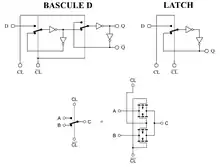

Chacun des quatre registres à décalage est constitué d'une chaîne de bascules D. Le premier et le troisième registre à décalage comptent quatre étages ; le second et le quatrième en comptent cinq. Les sorties des trois premiers étages des registres sont inaccessibles.

Le premier registre à décalage dispose d'une sortie latchée, sauf chez certains constructeurs.

Contrairement aux circuits 4006 d'autres fabricants, le premier registre à décalage ne présente pas de sortie latchée D1+4′. La broche correspondante (#2) est non connectée.

Entrées

L'entrée CLOCK (parfois abrégé en CLK) cadence l'ensemble des bascules du circuit. À l'instant où un front descendant (transition haut→bas) survient sur cette entrée, chacun des étages des registres voit l'état logique de son entrée recopié sur sa sortie. Un front montant (transition bas→haut) sur l'entrée CLOCK provoque la recopie de l'état logique de l'entrée du latch sur sa sortie.

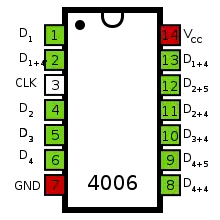

D1 (ou DATA1) est l'entrée du premier registre à décalage, constitué de quatre étages.

D2 (ou DATA2) est l'entrée du deuxième registre à décalage, constitué de cinq étages.

D3 (ou DATA3) est l'entrée du troisième registre à décalage, constitué de quatre étages.

D4 (ou DATA4) est l'entrée du quatrième registre à décalage, constitué de cinq étages.

Sorties

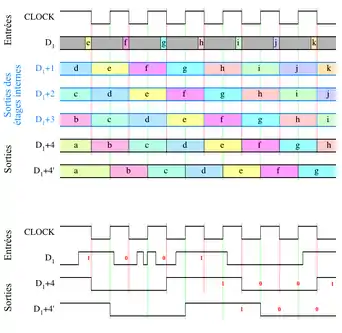

D1+4 (ou OUTD1+4) est la sortie du quatrième étage du premier registre à décalage. Lors d'un front descendant sur l'entrée CLOCK, elle prend l'état logique qui était présent sur l'entrée D1 trois fronts descendants de CLOCK plus tôt.

D1+4′ (ou OUTD1+4′) est la sortie latchée du quatrième étage du premier registre à décalage. Son état logique est actualisé à chaque front montant sur l'entrée CLOCK, de sorte qu'elle reproduit l'état de la sortie D1+4 avec un retard d'une demi-période de CLOCK.

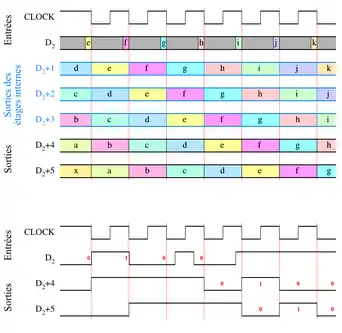

D2+4 (ou OUTD2+4) est la sortie du quatrième étage du deuxième registre à décalage. Lors d'un front descendant sur l'entrée CLOCK, elle prend l'état logique qui était présent sur l'entrée D2 trois fronts descendants de CLOCK plus tôt.

D2+5 (ou OUTD2+5) est la sortie du cinquième étage du deuxième registre à décalage. Lors d'un front descendant sur l'entrée CLOCK, elle prend l'état logique qui était présent sur l'entrée D2 quatre fronts descendants de CLOCK plus tôt.

D3+4 (ou OUTD3+4) est la sortie du quatrième étage du troisième registre à décalage. Lors d'un front descendant sur l'entrée CLOCK, elle prend l'état logique qui était présent sur l'entrée D3 trois fronts descendants de CLOCK plus tôt. Sur les circuits 4006 dépourvus de latch, la broche correspondante est non connectée (NC).

D4+4 (ou OUTD4+4) est la sortie du quatrième étage du quatrième registre à décalage. Lors d'un front descendant sur l'entrée CLOCK, elle prend l'état logique qui était présent sur l'entrée D4 trois fronts descendants de CLOCK plus tôt.

D4+5 (ou OUTD4+5) est la sortie du cinquième étage du quatrième registre à décalage. Lors d'un front descendant sur l'entrée CLOCK, elle prend l'état logique qui était présent sur l'entrée D4 quatre fronts descendants de CLOCK plus tôt.

Table de vérité

- Pour chaque étage de registre à décalage :

| Entrées | Sortie | |

|---|---|---|

| CLOCK | D | D+1 |

| 0 | x | Inchangé |

| ↑ | x | Inchangé |

| 1 | x | Inchangé |

| ↓ | 0 | 0 |

| ↓ | 1 | 1 |

- Pour le latch du premier registre à décalage (si présent) :

| Entrées | Sortie | |

|---|---|---|

| CLOCK | D1+4 | D1+4’ |

| 0 | x | Inchangé |

| ↑ | 0 | 0 |

| ↑ | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

| ↓ | 0 | 0 |

| ↓ | 1 | 1 |

| Notes : |

|---|

|

0 = niveau logique bas |

Chronogrammes

En bas, un exemple de signaux logiques obtenus.

En bas, un exemple de signaux logiques obtenus.

Brochage

Voir aussi

Articles connexes

Liens externes

Références

- (en) « CD4006B-MIL CMOS 18-Stage Static Shift Register | TI.com », sur www.ti.com (consulté le )

- (en) « CD4006BM/CD4006BC 18-Stage Static Shift Register - National Semiconductor, février 1988 » (consulté le )

- (en) « CMOS Integrated Circuits, Motorola, 1978 - page 7-18 », sur archive.org (consulté le )

- (en) « CMOS Integrated Circuits Databook, RCA, 1983 - page 66 », sur archive.org (consulté le )